I controller di memoria possono proteggere la memoria del PC. Controller di memoria dinamica Stati di base e modalità di funzionamento del dispositivo

Principi generali di organizzazione RAP. La modalità DMA è il modo più veloce per lo scambio, che viene implementato utilizzando hardware speciale: controller DMA senza l'uso di software. Per implementare la modalità PDP, il controllore deve eseguire una serie di operazioni sequenziali (Fig. 3.38):

I cicli DMA vengono eseguiti con celle di memoria posizionate in sequenza, quindi il controller DMA deve disporre di un contatore di indirizzi RAM. Il numero di cicli PDP è determinato da un contatore speciale. Lo scambio è controllato da un apposito circuito logico, che, a seconda del tipo di scambio, genera una coppia di segnali di controllo:  (leggi cicli),

(leggi cicli),  (scrittura cicli). Ne consegue che il controller DMA, su richiesta, deve assumere il controllo dei bus di sistema ed eseguire cicli combinati di lettura/uscita o scrittura/ingresso fino a quando il contenuto del contatore di cicli DMA è uguale a zero. Sulla fig. 3.38 mostra uno schema a blocchi dell'MPS con un controller PDP.

(scrittura cicli). Ne consegue che il controller DMA, su richiesta, deve assumere il controllo dei bus di sistema ed eseguire cicli combinati di lettura/uscita o scrittura/ingresso fino a quando il contenuto del contatore di cicli DMA è uguale a zero. Sulla fig. 3.38 mostra uno schema a blocchi dell'MPS con un controller PDP.

Il controller PDP K1810VT37 viene utilizzato come parte dell'MPS basato sugli MPC K580, K1810, K1821 per implementare l'accesso diretto alla memoria tramite quattro canali indipendenti con un incremento dell'indirizzo positivo o negativo a una velocità fino a 1,6 MB/s. KDPP ti consente di implementare il trasferimento di memoria-memoria, avendo ampie opportunità per il controllo del programma e il collegamento a cascata. Ogni canale può eseguire fino a 64K cicli DMA e ha la possibilità di inizializzazione automatica, ovvero ripetizione di cicli DMA con gli stessi parametri.

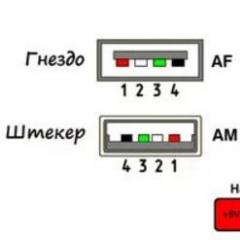

Scopo delle conclusioni di KPDP(Fig. 3.39).

CLK– ingresso per il collegamento del generatore di clock F CLK =3 MHz.

-Selezione del cristallo.

-Selezione del cristallo.  permette il lavoro del KPPP.

permette il lavoro del KPPP.

RIPRISTINA- Ripristina. Un segnale di alto livello ripristina l'RCAP impostando l'istruzione, la condizione, i registri di memorizzazione temporanea su zero e impostando tutti i bit della maschera su uno.

PRONTO- prontezza. Il segnale di ingresso utilizzato per sincronizzare il funzionamento del PDCA con i dispositivi ad azione lenta.

HLDA- Conferma di cattura. Il segnale di ingresso utilizzato dalla CPU per dire all'RPCH che può eseguire cicli RPCH.

DREQ3 – DREQ0 – input di richieste al RAP da dispositivi esterni. La polarità delle richieste è impostata a livello di codice. I segnali a questi ingressi devono essere mantenuti fino all'arrivo del segnale DACK. Nello stato iniziale, la priorità della richiesta è naturale, DREQ0 ha la priorità più alta.

DB7 – DB0 – un bus dati bidirezionale con un buffer di stato z. Nei cicli DMA, a queste righe vengono assegnate le otto cifre più significative del codice indirizzo, che devono essere “agganciate” al registro esterno con il segnale ADSTB. Nella modalità di funzionamento con la CPU, queste linee ricevono / trasmettono dati.

-lettura; come l'ingresso viene utilizzato dalla CPU per leggere il contenuto dei registri interni del CPAP; come uscita in modalità DMA consente l'uscita di dati da dispositivi esterni.

-lettura; come l'ingresso viene utilizzato dalla CPU per leggere il contenuto dei registri interni del CPAP; come uscita in modalità DMA consente l'uscita di dati da dispositivi esterni.

-disco; come l'input viene utilizzato dalla CPU per caricare i dati nei registri del CPAP; come uscita in modalità DMA permette di scrivere dati su registri di dispositivi esterni.

-disco; come l'input viene utilizzato dalla CPU per caricare i dati nei registri del CPAP; come uscita in modalità DMA permette di scrivere dati su registri di dispositivi esterni.

– fine del processo. Un input/output utilizzato per indicare la fine di un processo di trasferimento dati in modalità DMA. Applicando un segnale di basso livello a questo ingresso, è possibile interrompere il trasferimento dei dati. Al termine del trasferimento dei dati su uno dei canali, viene impostato un segnale in uscita

– fine del processo. Un input/output utilizzato per indicare la fine di un processo di trasferimento dati in modalità DMA. Applicando un segnale di basso livello a questo ingresso, è possibile interrompere il trasferimento dei dati. Al termine del trasferimento dei dati su uno dei canali, viene impostato un segnale in uscita  . Su questo segnale (esterno o interno), la richiesta viene rimossa e il servizio viene terminato. Se è impostata la modalità di inizializzazione automatica, i registri di lavoro di questo canale vengono caricati con il contenuto dei registri di base e i bit del registro della maschera non cambiano. Nelle modalità senza autoinizializzazione, i bit maschera e il bit TC nella parola di stato sono impostati in base allo stato del canale servito. Quando si trasferisce la memoria - uscita della memoria

. Su questo segnale (esterno o interno), la richiesta viene rimossa e il servizio viene terminato. Se è impostata la modalità di inizializzazione automatica, i registri di lavoro di questo canale vengono caricati con il contenuto dei registri di base e i bit del registro della maschera non cambiano. Nelle modalità senza autoinizializzazione, i bit maschera e il bit TC nella parola di stato sono impostati in base allo stato del canale servito. Quando si trasferisce la memoria - uscita della memoria  è orientato all'uscita e, al termine del conteggio, viene generato un segnale su questa uscita. Se uscita

è orientato all'uscita e, al termine del conteggio, viene generato un segnale su questa uscita. Se uscita  non viene utilizzato, deve essere collegato tramite una resistenza al bus di alimentazione (+5 V) per evitare la formazione di falsi segnali di fine processo.

non viene utilizzato, deve essere collegato tramite una resistenza al bus di alimentazione (+5 V) per evitare la formazione di falsi segnali di fine processo.

A3 - A0 - indirizzi ingressi/uscite. Vengono utilizzati come ingressi nella modalità di funzionamento della CPU e per indirizzare i canali ei registri dei canali dell'RCAP. In modalità DMA, sono uscite che trasportano i quattro bit meno significativi dell'indirizzo RAM.

A7 - A4– uscite di indirizzo, alle quali i bit corrispondenti dell'indirizzo RAM vengono trasferiti in modalità DMA. In modalità CPU, entrano nello stato z.

HRQ– Uscita richiesta presa pneumatici. Richiesta alla CPU di passare alla modalità DMA.

DACK3 – DACK0 - conferma del RAP. Righe di output a cui vengono inviati messaggi per la VU sulla possibilità di eseguire cicli DAP. La polarità del segnale è impostata dal software. Dopo il segnale di RESET, le uscite DACK vengono azzerate.

AEN- risoluzione dell'indirizzo. AEN=1 viene impostato al momento dell'emissione degli otto bit più significativi dell'indirizzo RAM sulla riga DB7 - DB0.

ADSTB– indirizzo stroboscopico. Un'uscita su cui si forma un impulso (strobo), che scrive i bit di ordine superiore (A15 - A8) dell'indirizzo RAM dai bus DB7 - DB0 in un registro buffer esterno.

- lettura dalla memoria. Un'uscita utilizzata in modalità DMA per controllare un'operazione di lettura della memoria.

- lettura dalla memoria. Un'uscita utilizzata in modalità DMA per controllare un'operazione di lettura della memoria.

- scrivere in memoria. Un'uscita utilizzata in modalità DMA per controllare un'operazione di scrittura della memoria.

- scrivere in memoria. Un'uscita utilizzata in modalità DMA per controllare un'operazione di scrittura della memoria.

u cc– bus di alimentazione (+5 V).

GND- generale.

Struttura del CPAP(Vedi Figura 3.39). Il controller include quattro canali, ciascuno dei quali è costituito da quattro registri a 16 bit.

Registra l'indirizzo attualeAUTO memorizza l'indirizzo corrente della cella di memoria durante l'esecuzione del ciclo DMA. Al termine del ciclo DMA, il contenuto di questo registro viene incrementato o decrementato di uno. Può essere letto o caricato con due comandi I/O. Il contenuto CAR può essere aggiornato su segnale  , se è programmata la modalità di autoinizializzazione.

, se è programmata la modalità di autoinizializzazione.

Registro dei cicli PDPCWR memorizza il numero di parole da trasmettere. Durante il caricamento di questo registro, ricordarsi che la costante in fase di caricamento deve essere maggiore del numero di parole necessarie per il trasferimento. Quando si eseguono cicli DAP, il registro opera in modalità contatore sottrattivo. Il bit TC del registro di stato viene impostato su uno nella transizione dallo stato zero allo stato FFFFH. La lettura e la scrittura del contenuto del registro avviene tramite due comandi input-output eseguiti in sequenza. Il contenuto del CWR può essere aggiornato mediante autoinizializzazione del segnale  oppure il valore FFFFH è memorizzato nel registro.

oppure il valore FFFFH è memorizzato nel registro.

Registro di archiviazione dell'indirizzo di baseSBARRAe il registro di memorizzazione per il numero base di cicli DAPWCR memorizzare i valori di base dell'indirizzo e il numero di cicli DAP, partecipare all'autoinizializzazione. Quando il controller PMA viene inizialmente caricato con i parametri iniziali, i registri CAR, BAR, CWR e WCR vengono scritti contemporaneamente. Durante l'esecuzione dei cicli PDP, il contenuto di BAR e WCR non cambia. È impossibile leggere lo stato di questi registri.

Inoltre, ogni canale ha un 6 bit registro modalitàSIG, che determina la modalità del suo funzionamento. Quando questo registro viene caricato, i bit meno significativi di D1, D0 indicano il codice del numero del canale. L'assegnazione dei bit MR è mostrata in fig. 3.40.

Con l'aiuto dei bit D2, D3, viene specificato uno dei tipi di trasmissione: lettura, scrittura, controllo. Questi bit possono assumere qualsiasi valore quando D6D7=11. Il bit D4 determina la modalità di caricamento automatico. Se D4=1, allora nella condizione di autoload CAR e CWR vengono caricati rispettivamente dai parametri BAR e WCR. Il bit D5 determina la modalità di cambio CAR. Se D5=0, dopo ogni ciclo RAP si verifica un aumento del contenuto del CAR; se D5=1, allora c'è una diminuzione. I bit D6, D7 determinano le modalità di funzionamento del canale: trasmissione su richiesta, trasmissione singola, trasmissione a blocchi, controller in modalità a cascata.

Il controller PMA include tre blocchi funzionali che svolgono funzioni di controllo. Buffer bus dati serve a coordinare il funzionamento del controllore con la CPU. Alcuni dei segnali che forniscono queste funzioni vengono utilizzati per controllare la trasmissione dei dati nei cicli DSP. Unità di controllo del controller durante il trasferimento di memoria - la memoria include una memoria temporanea di dati TR del registro a 8 bit, che fornisce la memorizzazione di un byte nella memoria del ciclo di trasferimento - memoria per il momento della modifica dell'indirizzo.

L'ultima parola caricata in questo registro viene memorizzata lì fino a quando non viene ricevuto un segnale di RESET. Unità di controllo modalità PDP genera i segnali di controllo necessari durante la trasmissione dei dati nei cicli DMA. Include due registri a 8 bit e due a 4 bit.

Registro di comandoCR determina i parametri principali del canale. Il CR viene caricato da un comando di uscita dalla CPU e ripristinato da un segnale RESET o da un comando di ripristino generale. Lo scopo dei bit di registro è mostrato in fig. 3.41. I bit D0, D1 vengono utilizzati per impostare le modalità di funzionamento dei canali 0 e 1 nella modalità memoria-memoria. Il bit D2 inizializza il controller per eseguire DMA, il bit D3 determina la modalità di esecuzione dei cicli DMA. Se D3=1, i cicli DMA vengono eseguiti con un salto di clock quando l'indirizzo cambia all'interno del byte basso. Il bit D4 imposta la modalità di priorità. Se D4=1, alla richiesta del canale di servizio viene assegnata la priorità più bassa - modalità di rotazione priorità. Il bit D5 imposta la modalità del ciclo di scrittura esteso. Se D5=1, segnala  prodotto con doppia durata. I bit D6, D7 programmano i livelli di richiesta dei segnali di conferma DMA (DREQ) e DMA (DACK).

prodotto con doppia durata. I bit D6, D7 programmano i livelli di richiesta dei segnali di conferma DMA (DREQ) e DMA (DACK).

Registro delle condizioniSR. I bit D3 - D0 di questo registro sono impostati dall'hardware quando si verifica un segnale TC, cioè dopo la fine dei cicli DMA o da un segnale esterno  . Questi bit vengono resettati (impostati a zero) dal segnale RESET e dopo che viene eseguito il comando di lettura del contenuto di questo registro. I bit D4 - D7 sono impostati dal software se è richiesta assistenza sul canale corrispondente. L'assegnazione dei bit SR è mostrata in fig. 3.42.

. Questi bit vengono resettati (impostati a zero) dal segnale RESET e dopo che viene eseguito il comando di lettura del contenuto di questo registro. I bit D4 - D7 sono impostati dal software se è richiesta assistenza sul canale corrispondente. L'assegnazione dei bit SR è mostrata in fig. 3.42.

Richiedi il registroRR. Il controllore può servire richieste di DMA generate sia dall'hardware - dagli ingressi DREQ, sia dal software - dallo stato dei bit (registri) delle richieste RR. Ciascun bit di questo registro corrisponde a una richiesta su uno dei canali. I bit di questo registro non sono mascherati e sono impostati separatamente da software o segnali TC e  . L'impostazione software di questi bit viene eseguita dal comando, il cui formato è mostrato in Fig. 3.43. Tutti i bit RR vengono resettati dal segnale RESET. Per elaborare una richiesta di programma, il controllore deve essere programmato in modalità di trasferimento a blocchi.

. L'impostazione software di questi bit viene eseguita dal comando, il cui formato è mostrato in Fig. 3.43. Tutti i bit RR vengono resettati dal segnale RESET. Per elaborare una richiesta di programma, il controllore deve essere programmato in modalità di trasferimento a blocchi.

Custodia per mascheraMASCHERA, con cui è possibile mascherare i segnali DREQ di ciascun canale. I bit MASK possono essere impostati da un apposito comando contemporaneamente (Fig. 3.44) o separatamente (Fig. 3.45). Inoltre, se il canale non è programmato per la modalità di caricamento automatico, dopo il segnale  il bit corrispondente del registro è impostato su uno. Tutti i bit MASK vengono impostati a zero dal segnale RESET o dal comando CMR (Clear Mask Register).

il bit corrispondente del registro è impostato su uno. Tutti i bit MASK vengono impostati a zero dal segnale RESET o dal comando CMR (Clear Mask Register).

Modalità operativa PDP. Il controller DMA può funzionare in due modalità principali: con la CPU ed eseguendo cicli DMA. Nella modalità di funzionamento con la CPU, il controller viene percepito da essa come un dispositivo esterno e dopo aver caricato le parole di controllo passa allo stato passivo S1. Il controller rimane in questo stato fino a quando non viene ricevuta una richiesta per un DREQ DMA all'ingresso di uno dei canali o questa richiesta non viene impostata dalla CPU in modo programmatico. Al rilevamento di una richiesta DMA, il controller entra nello stato S0 e asserisce il segnale di richiesta di acquisizione del bus di sistema HRQ, in attesa del segnale di conferma dell'acquisizione HLDA dalla CPU.Quando viene ricevuto il segnale HLDA, il controller inizia a eseguire i cicli DMA.

Ci sono quattro stati operativi durante questi cicli: S1 - S4. Se, durante l'esecuzione dei cicli DMA, viene applicato uno zero all'ingresso READY, il controllore esegue cicli di attesa SW tra i cicli S2/S3 e S4. Lo stato SW è caratterizzato dall'attività delle linee dati. Quando si trasferiscono informazioni in modalità memoria-memoria, è necessario eseguire due cicli completi di lettura e scrittura, quindi, per trasferire una parola, il controllore esegue due cicli DMA di quattro cicli ciascuno: S11 - S14 per la lettura dalla memoria e S21 - S24 per la scrittura in memoria.

Il diagramma temporale del funzionamento del controller in cicli PDP è mostrato in fig. 3.46. Nello stato passivo, gli ingressi di richiesta al RAP vengono interrogati ed è possibile l'interazione con la CPU utilizzando i consueti comandi input-output. Poiché l'interazione con la CPU è più spesso effettuata da una parola di due byte, il controllore utilizza un trigger interno per selezionarli correttamente, indicando un'operazione con il byte basso o alto della parola. Questo flip-flop viene ripristinato da un segnale RESET o da un comando di ripristino generale, che indica un'operazione a byte basso. Dopo aver eseguito un'operazione sul byte basso, viene impostato su uno, indicando il byte alto.

Il controller può essere programmato per eseguire le seguenti quattro modalità operative DMA. In modalità di trasmissione singola viene trasmesso un byte, mentre il contenuto del contatore di cicli DMA (CWR) viene decrementato e il contenuto del registro degli indirizzi (CAR) viene decrementato o incrementato di uno. Il bit Transmission End (TC) nel Condition Register è impostato su uno quando il contenuto del CWR è impostato su FFFFH. L'ingresso DREQ deve essere mantenuto attivo fino all'arrivo del segnale DACK. Se DREQ rimane attivo dopo che è stato trasmesso un byte, il segnale HRQ viene rimosso ed è possibile un nuovo ciclo di trasmissione con l'arrivo del segnale HLDA successivo.

In modalità trasferimento a blocchi I cicli DMA vengono eseguiti fino a quando il bit TC nel registro delle condizioni non viene impostato, ovvero quando il contatore di cicli DMA CWR assume il valore FFFFH o la trasmissione viene interrotta da un segnale esterno  . I cicli di trasmissione possono essere ripresi se il canale è stato programmato per l'inizializzazione automatica.

. I cicli di trasmissione possono essere ripresi se il canale è stato programmato per l'inizializzazione automatica.

In modalità su richiesta I cicli DMA continuano fino a quando non viene impostato il bit TC nel registro delle condizioni o il segnale  o il segnale DREQ non è deasserito.

o il segnale DREQ non è deasserito.

In questa modalità, la trasmissione può essere eseguita fino a quando il dispositivo esterno non completa la trasmissione delle informazioni. L'auto-inizializzazione in questa modalità può essere eseguita dopo la fine della trasmissione del segnale  , esterno o prodotto sulla base di TC.

, esterno o prodotto sulla base di TC.

Modalità di trasferimento da memoria a memoria consente di spostare blocchi di informazioni nel campo della RAM. Per implementare questa modalità vengono utilizzati i parametri dei canali 0 e 1. La trasmissione viene inizializzata via software impostando DREQ nel canale 0. Dopo l'arrivo del segnale HLDA=1, il controllore legge i dati dalla cella di memoria con l'indirizzo da il registro CAR del canale 0 in quattro cicli e li scrive nel registro di memoria temporanea TR , quindi, in quattro cicli, scrive questi dati in una cella di memoria con un indirizzo dal canale CAR 1. Quando il contenuto del registro di ciclo DMA CWR assume il valore FFFFH, il bit TC verrà impostato e il trasferimento terminerà. Il canale 0 può essere programmato per trasmettere informazioni senza modificare l'indirizzo, il che consente di riempire le celle del blocco RAM con una costante.

Tipi di trasmissione RAP. In tutte le modalità DMA sono possibili tre tipi principali di trasmissione. Registrazione dati- eseguito

trasferire i dati da un dispositivo esterno alla RAM. Il controller in questo caso attiva i segnali  .Lettura dei dati– i dati vengono trasferiti dalla RAM a un dispositivo esterno, i segnali sono attivati

.Lettura dei dati– i dati vengono trasferiti dalla RAM a un dispositivo esterno, i segnali sono attivati  . quando assegni o pseudo-bonifici il controller esegue le stesse azioni del ciclo di lettura/scrittura, ma non vengono generati segnali di controllo. In questo caso il segnale PRONTO non viene accettato. Inoltre, il controller può essere programmato per eseguire funzioni aggiuntive.

. quando assegni o pseudo-bonifici il controller esegue le stesse azioni del ciclo di lettura/scrittura, ma non vengono generati segnali di controllo. In questo caso il segnale PRONTO non viene accettato. Inoltre, il controller può essere programmato per eseguire funzioni aggiuntive.

Inizializzazione automatica viene eseguito se il bit corrispondente è impostato nel registro delle condizioni e da un segnale  . Durante l'autoinizializzazione, il contenuto dei registri di base BAR e WCR viene caricato nei registri del valore corrente CAR e CWR. I bit della maschera non cambiano. Dopo l'autoinizializzazione, il controller è pronto per il funzionamento e riprende il funzionamento con l'arrivo del segnale DREQ successivo. Per l'autoinizializzazione di entrambi i canali nella modalità memoria-memoria, i registri di ciclo DMA CWR devono essere programmati in modo identico.

. Durante l'autoinizializzazione, il contenuto dei registri di base BAR e WCR viene caricato nei registri del valore corrente CAR e CWR. I bit della maschera non cambiano. Dopo l'autoinizializzazione, il controller è pronto per il funzionamento e riprende il funzionamento con l'arrivo del segnale DREQ successivo. Per l'autoinizializzazione di entrambi i canali nella modalità memoria-memoria, i registri di ciclo DMA CWR devono essere programmati in modo identico.

Il controller può essere programmato per servire i canali con hard stabilire le priorità o dal loro cambiamento ciclico. Con una priorità codificata, la priorità più alta viene assegnata al canale con il numero più basso. In wraparound, la priorità più bassa viene assegnata al canale dopo che è stato servito. Ciò ti consente di servire tutti i canali a turno.

Tabella 3.3

|

Operazione |

|||||

|

Lettura del registro di stato |

|||||

|

Scrittura nel registro dei comandi di controllo |

|||||

|

Scrivendo al registro delle richieste |

|||||

|

Impostazione di tutti i bit della maschera |

|||||

|

Scrittura su Mode Register |

|||||

|

Impostazione della modalità di input a byte basso |

|||||

|

Leggi Holding Register |

|||||

|

Ripristino principale |

|||||

|

Ripristino di tutti i bit della maschera |

|||||

|

Impostazione del bit della maschera |

Programmazione del controllore. La programmazione del controllore viene eseguita dalla CPU tramite comandi I/O ed è possibile solo nello stato passivo o se è presente una tensione di basso livello all'ingresso HLDA, anche se è presente il segnale HRQ. L'inizializzazione iniziale del controllore deve essere effettuata subito dopo aver inserito la tensione di alimentazione per tutti i canali (anche se non utilizzati), caricando comandi e costanti. Gli indirizzi dei registri interni del controller sono determinati dal codice sui pin A3–A0. La Tabella 3.3 mostra i codici su A3–A0, corrispondenti ai comandi CPU eseguiti, e nella Tabella 3.4, i codici su A3–A0, corrispondenti agli indirizzi dei registri KPDP.

Tabella 3.4

|

Operazione |

|||||

|

Lettura del contenuto del canale CAR 0 |

|||||

|

Lettura del contenuto del canale CWR 0 |

|||||

|

Lettura del contenuto del canale CAR 1 |

|||||

|

Lettura del contenuto del canale 1 di CWR |

|||||

|

Lettura dei contenuti del canale CAR 2 |

|||||

|

Lettura del contenuto del canale 2 di CWR |

|||||

|

Lettura del contenuto del canale CAR 3 |

|||||

|

Lettura dei contenuti del canale CWR 3 |

Collegamento del controller al bus di sistema(Fig. 3.47). Gli otto bit più significativi dell'indirizzo vengono inviati al motore passo-passo e devono essere scritti dal segnale ADSTB su un registro esterno. La linea AEN viene utilizzata per garantire che i bit di indirizzo rimangano validi sullo SHA per tre periodi di clock del ciclo DMA. Le linee A7 - A0 sono collegate direttamente alla SHA. I segnali MEMR, MEMW, IOR, IOW controllano rispettivamente la RAM e il buffer VU nei cicli DMA.

KPDP a cascata. Un esempio di utilizzo in cascata del PDCA può essere un IBM PC / AT, in cui un secondo 8237A è stato collegato al bus di indirizzi con un offset di 1 byte (Fig. 3.48). I suoi registri di indirizzi a 16 bit sono in grado di pilotare le linee di indirizzi A16 - A1 (il byte basso di A0 è sempre 0). Pertanto, il secondo PDCH fornisce la trasmissione di due byte. Il secondo chip 8237A è collegato come master e crea tre canali DMA a 16 bit.

Domande e compiti

3.37. Quali sono le modalità operative del KPPP e le sue funzioni nel sistema?

Definire registri accessibili tramite software e il loro indirizzamento.

Fare uno schema di collegamento di K1810BT37 all'indirizzo e ai bus dati dell'MPS.

Comporre un programma di inizializzazione del controller per lo scambio di blocchi su un canale.

Spiegare l'implementazione della modalità PDP su VT37.

Spiegare l'indirizzamento dei registri KPDP durante la programmazione.

Come viene formato l'indirizzo a 16 bit dell'RCAP durante il controllo dello scambio?

Spiegare la fornitura di RRP su richieste da un RPCS slave.

Quali priorità di richiesta supporta l'8237 (BT37)?

In quale sequenza è necessario caricare i registri del controllore durante la programmazione?

Embedded Flash Controller (EFC) fa parte del Memory Controller (MC) e fornisce un'interfaccia per accedere ai blocchi di memoria flash su un bus interno a 32 bit. Ciò consente di aumentare notevolmente la velocità di recupero delle istruzioni dalla memoria flash quando il core del processore funziona in modalità Thumb (sistema di istruzioni a 16 bit) grazie al funzionamento del buffer a 32 bit. Inoltre, il controller flash integrato supporta una serie completa di comandi per leggere, scrivere, cancellare la memoria flash, impostare e cancellare i bit di sicurezza.

20.2 Descrizione funzionale

20.2.1 Organizzazione della memoria flash incorporata

Le interfacce di memoria flash integrate sono collegate direttamente a un bus interno a 32 bit basato su molte delle seguenti interfacce.

- Semplice organizzazione della memoria: più pagine della stessa dimensione.

- Due buffer di lettura a 32 bit progettati per aumentare la velocità di lettura della flash (consultare "Comandi di lettura" a pagina 101).

- Un buffer di scrittura per memorizzare i dati durante la programmazione di una pagina flash. Questo buffer ha le dimensioni di una pagina ed è di sola scrittura. Inoltre, il buffer di scrittura indirizza l'intera area di 1 MB di memoria flash (vedere "Comandi di scrittura" a pagina 101).

- Diversi bit di sicurezza (bit di blocco) per impedire la cancellazione e la scrittura della memoria flash. Ogni area protetta della memoria flash (tutte le aree sono della stessa dimensione) è costituita da un numero fisso di pagine poste in sequenza. Ciascuna di queste aree è direttamente associata a un solo bit di sicurezza.

- Alcuni bit di memoria non volatile - bit NVM (Non Volatile Memory) per scopi generali. Ciascuno di questi bit è responsabile del controllo di determinati nodi del microcontrollore. Per ulteriori informazioni su ciascun bit NVM, vedere i capitoli pertinenti di questo documento.

Tabella 20-1. Numero di bit di sicurezza e bit NVM per uso generico per i membri della famiglia AT91SAM7S

Figura 20-1. Mappa della memoria flash incorporata

20.2.2 Leggi i comandi

Per accelerare il processo di lettura della memoria flash, nel controller EFC è integrato un buffer a 32 bit dedicato. A causa della presenza di questo buffer, quando il processore opera in modalità Thumb (sistema di istruzioni a 16 bit), l'accesso alla memoria flash avviene due volte più raramente, per cui aumenta la frequenza di recupero delle istruzioni e, di conseguenza, aumenta la velocità del processore (Fig. 20-2, Fig. 20-3 e Fig. 20-4).

Questa ottimizzazione viene eseguita solo durante il recupero delle istruzioni e non durante la lettura dei dati dalla memoria flash.

I comandi di lettura possono essere eseguiti con o senza cicli di attesa aggiuntivi. È possibile impostare fino a tre cicli di attesa (inclusi) nel campo FWS (Flash Wait State) del Flash Mode Register MC_FMR (vedere "Flash Mode Register", pagina 110). Con FWS = 0, si accede alla memoria flash incorporata in un ciclo.

L'accesso alla memoria flash è disponibile a 32 bit (dizionario), 16 bit (mezza parola) e 8 bit.

Poiché la dimensione della memoria flash incorporata è inferiore a quella del microcontrollore rispetto alla dimensione dello spazio degli indirizzi della memoria interna assegnata ad esso (1 MB), il controller di memoria implementa il cosiddetto. duplicazione di questo blocco di memoria flash in tutto lo spazio di indirizzi ad esso assegnato. Ad esempio, per l'AT91SAM7S64, la memoria flash da 64 KB è mappata esattamente 1024/64 = 16 volte in questo spazio di indirizzi.

Figura 20-2. Ottimizzazione durante la lettura del codice di comando in modalità Thumb per FWS = 0

Figura 20-3. Ottimizzazione durante la lettura del codice di comando in modalità Thumb per FWS = 1

Figura 20-4. Ottimizzazione durante la lettura del codice di comando in modalità Thumb per FWS = 3

20.2.3 Scrivi comandi

L'area di memoria interna riservata alla memoria flash incorporata può anche essere scritta solo tramite un buffer dedicato. Quando si eseguono comandi di scrittura flash, vengono presi in considerazione solo gli 8 bit inferiori dell'indirizzo (poiché si tratta di dati a 32 bit, vengono effettivamente presi in considerazione i 10 bit inferiori dell'indirizzo). A loro volta, i 10 bit superiori dell'indirizzo dell'area interna (1 MB) riservata alla memoria flash indirizzano questo cosiddetto. una finestra di 256 parole (1024 byte). Pertanto, tutta questa memoria interna è composta da 1024 finestre di questo tipo.

Qualsiasi comando di scrittura sulla memoria flash integrata può essere disabilitato dalla MPU (Memory Protection Unit).

La memoria flash può essere scritta solo in parole (32 bit), quindi qualsiasi tentativo di scrivere mezze parole (16 bit) o byte (8 bit) produrrà un risultato imprevedibile.

I comandi di scrittura accettano il numero di cicli di attesa (campo FWS in MC_FMR) specificato per i comandi di lettura, più un ciclo aggiuntivo, tranne quando FWS = 3 (vedere "Registro modalità flash", pagina 110).

20.2.4 Set di comandi del controller flash

EFCS include comandi per la programmazione della memoria flash, comandi per l'impostazione della protezione (non protezione) delle sue aree, comandi per la programmazione sequenziale e l'impostazione della protezione della memoria flash e un comando per la cancellazione completa di tutta la memoria flash.

Tabella 20-2. Sistema di comando del controller flash

Prima di eseguire uno di questi comandi, il campo FCMD del registro MC_FCR deve essere impostato sul codice per quel comando. Poiché MC_FCR è di sola lettura, il flag FRDY viene automaticamente cancellato. Al termine dell'esecuzione dell'istruzione, viene impostato automaticamente il flag FRDY, che può attivare l'interrupt corrispondente se abilitato tramite il controller di memoria (MC).

Tutte le istruzioni flash sono protette dall'esecuzione accidentale utilizzando una parola chiave comune (parola chiave), che deve essere specificata negli 8 bit superiori del registro MC_FCR ogni volta che viene eseguita l'istruzione successiva.

Un'istruzione con una parola chiave specificata in modo errato e/o un codice specificato in modo errato per tale istruzione non verrà eseguita, anche se è impostato il flag PROGE nel registro MC_FSR. Questo flag verrà ripristinato automaticamente alla successiva lettura del registro MC_FSR.

Un tentativo di scrittura o cancellazione di una pagina che si trova in un'area protetta non avrà alcun effetto sul contenuto della memoria flash (questo comando verrà infatti ignorato), anche se è impostato il flag PROGE nel registro MC_FSR. Questo flag verrà ripristinato automaticamente alla successiva lettura del registro MC_FSR.

Figura 20-5. Diagramma di flusso dei comandi

Per una corretta esecuzione dei comandi flash, il campo Cycle Time in Microseconds (FMCN) nel Flash Controller Mode Register (MC_FMR) deve essere impostato sul valore corretto (vedere "Flash Controller Mode Register", pagina 110).

20.2.4.1 Programmazione flash

Bastano pochi comandi per programmare la memoria flash.

Secondo la tecnologia della memoria flash, deve essere cancellata immediatamente prima del processo di programmazione. È possibile cancellare un'intera area flash o una singola pagina cancellando il flag NEBP nel registro MC_FMR scrivendo direttamente il codice dell'istruzione nel registro MC_FCR.

Impostando il flag NEBP nel registro MC_FMR, una pagina può essere programmata in un certo numero di passi se è già stata cancellata in anticipo (vedi Figura 20-6).

Figura 20-6. Esempio di programmazione di una sezione di una pagina Flash

Al termine del processo di programmazione, la pagina può essere protetta da cancellazioni o scritte accidentali o intenzionali (quando l'intera area di appartenenza di questa pagina è protetta). Utilizzando il comando WPL, la protezione può essere impostata automaticamente subito dopo la fine di un ciclo di scrittura della pagina.

I dati scritti vengono archiviati in un buffer interno, la cui dimensione è uguale alla dimensione di una pagina flash. Questo buffer interno copre l'intero spazio degli indirizzi della flash interna, ad es. infatti, può essere visualizzato nella sua interezza in una qualsiasi delle sue pagine.

Nota:è vietato scrivere byte (8 bit) o mezze parole (16 bit), perché in quanto provoca la corruzione dei dati registrati.

Il processo di scrittura dei dati nella memoria flash precedentemente allocata nel buffer interno è controllato dal registro dei comandi flash (MC_FCR). Di seguito è riportata la sequenza di lavoro con questo registro.

- Un'intera pagina di scrittura, che può essere posizionata a qualsiasi indirizzo all'interno dell'intero spazio di indirizzi flash, è possibile solo come dizionario (dati a 32 bit).

- Il ciclo di scrittura della pagina inizia immediatamente dopo che il numero di pagina e il codice del comando di scrittura stesso sono stati specificati nel registro MC_FCR. Questo cancella automaticamente il flag FRDY nel registro di stato della programmazione Flash (MC_FSR).

- Immediatamente dopo il completamento di un ciclo di programmazione, il flag FRDY viene impostato nel Registro di stato della programmazione Flash (MC_FSR). Se gli interrupt dal flag FRDY sono abilitati, il segnale di interrupt appropriato si verificherà nel controller di memoria (MC).

- Errore di programmazione: è stata scritta una parola chiave non valida nel registro MC_FSR e/o è stato specificato un comando non valido.

20.2.4.2 Cancellazione completa del comando flash

Tutta la memoria flash su chip può essere cancellata se il registro MC_FCR viene scritto con il comando "Cancella tutto" - EA (Cancella tutto).

La cancellazione dell'intera memoria flash è possibile solo quando nessuna delle sue aree è protetta dalla cancellazione e dalla scrittura (nessuno dei flag di protezione della memoria flash è impostato). In caso contrario (almeno uno dei flag di protezione è impostato) questo comando verrà ignorato. Se è impostato il flag LOCKE nel registro MC_FMR, si verificherà il segnale di interruzione corrispondente.

Il flag FRDY verrà impostato automaticamente nel registro MC_FSR dopo la cancellazione dell'ultimo comando di programmazione o della memoria flash. In questo caso, all'uscita del controller di memoria (MC), comparirà immediatamente il segnale di interruzione corrispondente, se abilitato.

Durante l'esecuzione del ciclo di programmazione possono verificarsi errori che vengono registrati nel registro MC_FSR. Questi errori sono elencati di seguito.

- Errore di programmazione: è stata scritta una parola chiave non valida nel registro MC_FSR e/o è stato specificato un comando non valido.

- Errore di blocco: è stato effettuato un tentativo di programmare un'area protetta. Per programmare correttamente quest'area, è necessario prima sproteggerla utilizzando il comando unprotect.

20.2.4.3 Bit di protezione flash

Ciascuno dei bit di sicurezza è legato a un'area specifica della memoria flash, costituita da un numero specifico di pagine. Lo scopo di questi bit è proteggere la memoria flash da cancellazioni/programmazioni accidentali o intenzionali.

Durante il processo di fabbricazione del microcontrollore, alcuni dei bit di protezione possono essere impostati al suo interno. Il loro scopo è proteggere una determinata area di memoria flash, che per impostazione predefinita contiene un programma scritto sul microcontrollore durante la sua produzione. Prima di programmare/cancellare un'area protetta, questa deve essere sprotetta.

Di seguito è riportato l'ordine in cui è impostata la protezione per un'area:

Nel registro di comando flash deve essere scritto il seguente valore: (0x5A dopo il completamento del comando di protezione, verrà impostato il flag FRDY nel registro MC_FSR. In questo caso comparirà immediatamente il segnale di interrupt corrispondente all'uscita della memoria controller (MC), se abilitato. ul>

Dopo che la protezione è stata impostata, può essere non protetta, la seguente è la sequenza di annullamento della protezione di un'area:

- Nel Flash Command Register deve essere scritto il seguente valore: (0x5A, dopo l'esecuzione del comando di protezione verrà impostato il flag FRDY nel registro MC_FSR. In questo caso comparirà immediatamente il segnale di interrupt corrispondente all'uscita del controller di memoria (MC), se abilitato.

Se si verifica un errore durante l'esecuzione del comando (una parola chiave non valida e/o un codice di comando errato è specificato nel registro MC_FCR), questo fatto verrà registrato nel registro MC_FSR.

L'esecuzione del comando per cancellare un bit di blocco scrive fisicamente un "1" nel bit corrispondente, sebbene la lettura del registro MC_FSR legga il bit LOCKx corrispondente come "0". Al contrario, l'esecuzione di un comando lock bit set scrive fisicamente uno "0" nel bit corrispondente e la lettura del registro MC_FSR legge il bit LOCKx corrispondente come "1".

Nota: indipendentemente dal fatto che la memoria flash sia protetta, è comunque possibile accedervi tramite lettura.

20.2.4.4 Bit NVM per uso generale

I bit per uso generico - bit NVM - non sono associati alla memoria flash incorporata, ma hanno lo scopo di proteggere altri nodi del microcontrollore. Ciascuno di questi bit può essere impostato (cancellato) indipendentemente dagli altri. Per i dettagli sui bit NVM, vedere i capitoli pertinenti di questo documento.

Quella che segue è la sequenza di attivazione per i bit NVM generici.

- Esecuzione del comando Set General Purpose NVM Bit (SGPB) scrivendo nel Flash Memory Command Register (MC_FCR) il codice di questo comando e il numero di questi bit nel campo PAGEN dello stesso registro.

- dopo il completamento dell'istruzione SGPB, verrà impostato il flag FRDY nel registro MC_FSR. In questo caso, all'uscita del controller di memoria (MC), comparirà immediatamente il segnale di interruzione corrispondente, se abilitato.

Durante l'esecuzione del ciclo di programmazione possono verificarsi errori che vengono registrati nel registro MC_FSR. Questi errori sono elencati di seguito.

- Il campo PAGEN del registro MC_FCR indica il numero di bit di uso generale che è maggiore del numero massimo consentito di bit NVM implementati nel chip. Di seguito è riportata la sequenza per cancellare i bit NVM generici.

- Esecuzione del comando Clear General Purpose NVM Bit (CGPB) scrivendo nel Flash Command Register (MC_FCR) il codice comando e il numero di questi bit nel campo PAGEN dello stesso registro.

- al termine dell'istruzione CGPB, verrà impostato il flag FRDY nel registro MC_FSR. In questo caso, all'uscita del controller di memoria (MC), comparirà immediatamente il segnale di interruzione corrispondente, se abilitato.

Durante l'esecuzione del ciclo di programmazione possono verificarsi errori che vengono registrati nel registro MC_FSR. Questi errori sono elencati di seguito.

- Errore di programmazione: è stata scritta una parola chiave non valida nel registro MC_FSR e/o è stato specificato un comando non valido.

- Il campo PAGEN del registro MC_FCR indica il numero di bit di uso generale che è maggiore del numero massimo consentito di bit NVM implementati nel chip.

L'esecuzione di un comando "cancella bit per uso generico NVM" scrive fisicamente un "1" nel bit corrispondente, sebbene la lettura del registro MC_FSR legga il bit GPNVMx corrispondente come "0". Al contrario, l'esecuzione del comando "Set NVM General Purpose Bits" scrive fisicamente "0" nel bit corrispondente e la lettura del registro MC_FSR legge il bit GPNVMx corrispondente come "1".

Nota: indipendentemente dallo stato dei bit NVM generici, la memoria flash è sempre leggibile.

20.2.4.5 Bit di sicurezza

Il bit segreto ha lo scopo di impedire tentativi esterni di accedere al bus di sistema interno. Dopo aver impostato il bit di sicurezza, è vietato il funzionamento dell'interfaccia JTAG, dell'interfaccia di programmazione rapida della memoria flash e l'accesso alla memoria flash tramite l'interfaccia seriale. L'accesso alla memoria flash tramite le interfacce di cui sopra è nuovamente consentito solo quando il cristallo è completamente cancellato tramite il pin ERASE esterno - vedere il capitolo 4. Assegnazione dei pin. Quando il pin ERASE viene portato in alto (vedere la sezione 7.4. "Cancella pin di controllo"), tutti i flash sul chip, tutti i bit di protezione flash e tutti i bit NVM per uso generico vengono cancellati e solo dopo aver eseguito tutto ciò cancellando il bit di privacy .

Di seguito è riportata la sequenza per l'impostazione del bit di privacy.

- Eseguire il comando Set Security Bit (SSB) scrivendo il codice del comando nel Flash Command Register (MC_FCR).

- dopo il completamento dell'istruzione SSB, verrà impostato il flag FRDY nel registro MC_FSR. In questo caso, all'uscita del controller di memoria (MC), comparirà immediatamente il segnale di interruzione corrispondente, se abilitato.

Immediatamente dopo aver impostato il bit di sicurezza, il flag SECURITY verrà impostato nel registro MC_FSR.

Nucleo del processore dei microcontrollori:

- Unità logica aritmetica

- organizzazione della memoria

Buon giorno cari radioamatori!

Ti do il benvenuto nel sito ""

Oggi (più precisamente, nel corso di diversi articoli), daremo un'occhiata più da vicino base qualunque microcontrollore – nucleo del processore.

Elementi principali:

1. Unità logica aritmetica

ALU- il cuore (e forse la mente, con onore e coscienza) del microcontrollore.

Qui non entreremo nel ruolo di uno "smembramento maniacale" e di curiosare negli interni di questo dispositivo. Impariamo solo che grazie all'ALU si svolge tutto il lavoro del microcontrollore. Se mai hai il desiderio di imparare più a fondo come funziona il "cuore" del microcontrollore (e sarà bello se apparirà), allora nei libri dei meravigliosi autori Belov, Ryumik, Evstifeev, Revich, Baranov e molti altri troverai sempre una risposta dettagliata.

2. Memoria del microcontrollore (organizzazione della memoria)

Prima di considerare la memoria del microcontrollore, parliamo un po' della memoria in generale.

La memoria umana - tutto è chiaro con essa - può essere "solida" (quando hai una memoria solida e talvolta anche sana di mente) e, purtroppo, "fuggente". E tutte le informazioni sono memorizzate nei cosiddetti "neuroni" - piccole celle di memoria.

Quasi tutto è lo stesso con i microcontrollori. Solo se una persona ha la cella più piccola per la memorizzazione di informazioni chiamata "neurone", allora la cella di memoria più piccola per un microcontrollore per memorizzare le informazioni si chiama " po“.

Un bit può memorizzare un uno logico o uno zero logico.

Po

– l'unità di misura minima per la quantità di memoria nella tecnologia dei microprocessori.

La prossima unità di memoria principale, o più comune, è byte.

Byte – sono otto bit di informazioni. Un byte può memorizzare solo otto zeri e uno.

Il numero massimo che può essere scritto in un byte è 255. Se operi con numeri grandi nel programma, allora dovresti sapere (per sapere quanti byte sono necessari per memorizzare il numero) che il numero massimo che può essere scritto a:

– un byte = 255

– due byte = 65535

– tre byte = 16 777 215

- quattro byte - un numero superiore a 4 miliardi (se non sei almeno un centinaio della rivista Forbes, non avrai bisogno di quattro byte di memoria per memorizzare i numeri).

La scrittura in memoria e la lettura dalla memoria avvengono in byte (non è possibile scrivere o leggere un bit di informazioni).

La prossima unità di misura è kilobyte.

Ci sono 1024 byte di informazioni in un kilobyte.

(esattamente 1024, non 1000 byte).

Esistono anche grandi valori per misurare la quantità di memoria (megabyte, gigabyte), ma non sono ancora utilizzati nei microcontrollori.

Spero che tutto ci sia chiaro con le unità di misura della memoria elettronica:

Organizzazione della memoria nel microcontrollore

I chip AVR hanno tre tipi di memoria:

– memoria di programma, nota anche come memoria FLASH

– memoria dati, nota anche come RAM

(RAM)alias SRAM

– memoria non volatile, alias EEPROM, alias EEPROM

Il microcontrollore ha tre spazi di indirizzi in cui si trovano i suddetti tipi di memoria. Allo stesso tempo, la memoria dei dati (in termini di spazio di indirizzi allocato) si è rivelata un po' deprivata: deve condividere il suo spazio di indirizzi con celle di memoria che memorizzano registri generici e registri I / O (imparerai in dettaglio nel prossimo articolo). Questi registri non appartengono fisicamente alla memoria dati, ma si trovano nello stesso spazio di indirizzi. Se gli indirizzi iniziali della memoria di programma e della memoria non volatile iniziano all'indirizzo zero, l'indirizzo iniziale della memoria dati non inizia all'indirizzo zero - i registri generici e i registri I/O prendono il loro posto dall'indirizzo zero e solo loro sono seguiti dagli indirizzi delle celle di memoria del programma.

Alcuni tipi di MCU ATiny non dispongono di memoria dati.

Memoria di programma (memoria FLASH)

Memoria di programmaè progettato per memorizzare i nostri programmi al suo interno, così come tutti i dati di cui abbiamo bisogno che non cambiano durante l'esecuzione del programma (costante). Quando l'alimentazione del microcontrollore viene spenta, tutti i dati nella memoria del programma vengono salvati.

Memoria di programma, ovviamente, hanno tutti i microcontrollori. La dimensione della memoria del programma, a seconda del tipo di MK, varia da 1 kilobyte a 256 kilobyte.

Accesso alla memoria del programma solo il programmatore ha durante la programmazione dell'MK, l'MK stesso ha anche accesso alla memoria del programma, ma solo per leggere i dati dalla memoria, non può scrivere nulla lì (non si sa mai, improvvisamente vuole rovinare il nostro programma). È vero, l'MK della famiglia Mega ha l'opportunità (con il permesso del programmatore) di apportare modifiche alla memoria del programma, ma questa è un'altra storia.

Per la memoria di programma, ci sono altri due tipi di misurazione della memoria: " parola" e " pagina“.

Il fatto è che la memoria del programma è costituita da celle composte da due byte. Tale cellula è chiamata "parola". E questo viene fatto in questo modo perché quasi tutti i comandi MK sono costituiti da due byte e, di conseguenza, sono necessari due byte nella memoria del programma per scriverli. Ogni comando MK è una "parola". Esistono diversi comandi che richiedono 4 byte di memoria per la scrittura: due parole, ma tali comandi si trovano in MK con memoria di programma maggiore di 8 kilobyte.

Così, in una cella della memoria di programma può essere scritto:

- qualsiasi comando composto da due byte

- metà del comando, composto da 4 byte

- due costanti, ognuna delle quali si inserisce in un byte, o una costante a sedici bit. Tuttavia, se scrivi tre costanti a un byte in memoria, occuperanno comunque quattro byte (due parole) in memoria.

Oltretutto, la scrittura nella memoria di programma avviene non solo per “parole”, ma anche per “pagine”

. Dimensioni della pagina va da 64 a 256 byte (maggiore è la quantità di memoria del programma, maggiore è la “pagina”). Cosa significa. Se hai creato un piccolo programma lungo 11 parole (22 byte), occuperà comunque una pagina di memoria del programma, ad es. almeno 64 byte. I 42 byte "extra" verranno riempiti con zeri o uno. Queste sono le torte.

Ma non è tutto.

La memoria del programma può avere tre stati(se così posso dire):

1. Tutta la memoria è a disposizione del programmatore

In questo caso, possiamo riempire completamente tutta la memoria con il nostro programma e i nostri dati. E il programma partirà dall'indirizzo di memoria zero.

2. Parte della memoria occupa MK

Nel caso in cui MK venga utilizzato durante il funzionamento (e spero che vi ricordiate di cosa si tratta), MK prende parte della memoria per le esigenze di elaborazione degli interrupt e la memorizza al suo interno” vettori di interruzione“.

Cos'è.

Quando consentiamo all'MK di elaborare gli interrupt, esso, partendo dall'indirizzo zero della memoria, prende alcune celle per memorizzare gli indirizzi in esse, a cui l'MK deve andare per eseguire la routine di interrupt. Per ogni interrupt, l'MK alloca due byte di memoria (una parola) che memorizzano gli indirizzi delle routine di interrupt. Questi indirizzi, che indicano dove si trova in memoria la subroutine per elaborare questo o quell'interrupt, sono chiamati “ vettori di interruzione“. E viene chiamata l'intera area della memoria in cui sono memorizzati i "vettori di interruzione" interrompere la tabella dei vettori. Il numero di celle di memoria occupate per gli interrupt dipende direttamente dal numero di possibili interruzioni per un dato microcontrollore (da poche a diverse dozzine). Tutti gli interrupt si trovano all'inizio della memoria di programma, dall'indirizzo zero, e hanno una sequenza chiara. All'indirizzo zero si trova sempre il vettore di interrupt reset. Quando si accende il dispositivo o si ripristina con il pulsante, viene attivato l'interruzione di ripristino. Il MK legge dall'indirizzo zero (dalla cella) l'indirizzo che indica dove in memoria si trova l'inizio del nostro programma, e andando a questo indirizzo inizia l'esecuzione del programma. Il programma stesso in questo caso si troverà nella memoria del programma subito dopo la tabella degli interrupt.

3. MK prende un'altra parte della memoria del programma (più precisamente, non occupa, ma alloca un'area alla fine della memoria, in cui il programmatore inserisce un programma speciale: il "caricatore").

Ciò è possibile negli MCU della famiglia "MEGA", che hanno la capacità di consentire all'MCU di apportare modifiche alla memoria del programma. Cosa significa.

Alcuni MK hanno la capacità autoprogramma. Nella pratica dei dilettanti, questa possibilità di MK viene utilizzata molto raramente. La capacità di riprogrammazione (autoprogrammazione) è necessaria principalmente nei casi di produzione industriale di un dispositivo su microcontrollore, per il quale può poi essere rilasciato un aggiornamento software. Non prenderemo in considerazione questa possibilità, almeno non ancora. Dobbiamo solo sapere che negli MK che supportano l'autoprogrammazione, la memoria del programma è divisa in due parti

:

- superiore - sezione del programma applicativo, dove si trova il nostro programma e interrompi i vettori

- minore - sezione bootloader (Sezione caricatore di avvio- in inglese), dove il programmatore posiziona il suo programma di caricamento. La dimensione della sezione del bootloader dipende dalla dimensione totale della memoria del programma MK e può variare da 128 byte a 4096 byte. Se non utilizziamo la possibilità di autoprogrammazione dell'MK, questa sezione viene fornita per il nostro programma e i nostri dati.

Ebbene, la memoria FLASH è chiamata memoria di programma perché è realizzata utilizzando la cosiddetta tecnologia Flash (come le solite “flash drive” per computer per tutti noi).

La memoria del programma consente 10.000 cicli di riprogrammazione.

Memoria dati (RAM statica, SRAM)

RAM, è memoria dati genere SRAM, progettato per memorizzare in esso vari dati ottenuti a seguito del programma.

Quando si spegne l'alimentazione del microcontrollore, tutti i dati in esso memorizzati vengono persi.

Memoria datiè disponibile in quasi tutti i microcontrollori (assente nei MK più semplici della famiglia Tiny).

In tutti gli MC della famiglia Mega (e parte degli MC della famiglia Tiny), la quantità di memoria dati incorporata varia da 128 byte a 8 kilobyte e quasi tutta è data a nostra completa disposizione. Basta un po' di MK per organizzare lo stack (scopriremo di cosa si tratta più avanti). Alcuni MK prevedono il collegamento di memoria esterna (può essere di qualsiasi tipo - FLASH, SRAM, EEPROM) fino a 64 kilobyte. Nel caso di collegamento di memoria esterna in tali MK, diventa, per così dire, una continuazione della memoria di dati.

La scrittura e la lettura dalla memoria dati avviene byte per byte e, a differenza della memoria di programma, non è divisa in pagine e parole.

Memoria non volatile (EEPROM)

Memoria non volatile si riferisce anche alla memoria dati, ma a differenza di quest'ultima ha diverse caratteristiche. Ha lo scopo di memorizzare dati e costanti che devono essere conservati in assenza di alimentazione.

Tutti i microcontrollori hanno EEPROM.

Allo spegnimento dell'alimentazione del microcontrollore, tutti i dati archiviati nella memoria non volatile vengono salvati (per questo viene chiamata non volatile).

La quantità di memoria non volatile, a seconda del tipo di MK, varia da 64 byte a 4 kilobyte.

Scrivere e leggere informazioni in memoria viene eseguito byte per byte. Tuttavia, nei modelli precedenti della famiglia MEGA, la memoria non volatile, così come la memoria di programma, ha un record di pagina. La dimensione della pagina è piccola, solo 4 byte. In pratica, questa caratteristica non ha importanza: sia la scrittura che la lettura vengono comunque eseguite byte per byte.

Numero di cicli di scrittura e cancellazione la memoria raggiunge 100.000.

La caratteristica principale della EEPROM è che quando i dati vengono scritti su di essa, diventa molto "lenta": la scrittura di un byte può durare da 2 a 4 millisecondi (questa è una velocità molto bassa) e può accadere, ad esempio, che alcuni - o interruzione, in tal caso il processo di scrittura dei dati sarà rovinato.

Inoltre, non è consigliabile scrivere dati nella memoria non volatile dall'indirizzo zero (non ricordo la fonte di queste informazioni, ma ricordo esattamente cosa ho letto da qualche parte) - i dati potrebbero essere danneggiati durante il funzionamento dell'MK . A volte i programmatori fanno un passo indietro di alcuni byte dall'inizio della memoria e solo nelle celle successive iniziano a scrivere i dati.

Oggi nel mondo civile difficilmente troverai una persona che non ha mai usato un computer e non ha idea di cosa sia. Pertanto, invece di parlare ancora una volta delle parti note di questo complesso sistema, ti parleremo di qualcosa che ancora non conosci. Discuteremo e forniremo una breve descrizione dei controller di memoria, senza i quali il funzionamento del computer sarebbe impossibile. Se vuoi capire il sistema del tuo personal computer o laptop, devi saperlo. E quindi, discutiamo oggi di cosa sono i controller di memoria.

Il compito che devono affrontare i controller di memoria del computer è molto importante per il funzionamento del computer. Il controller di memoria è un chip che si trova sulla scheda madre o sull'unità di elaborazione centrale. La funzione principale che svolge questo minuscolo chip è controllare il flusso di dati, sia in entrata che in uscita. La funzione secondaria del controller di memoria è aumentare le potenzialità e le prestazioni del sistema, nonché l'uniforme e corretta collocazione delle informazioni nella memoria, disponibile grazie ai nuovi sviluppi nel campo delle nuove tecnologie.

La posizione del controller di memoria nel computer dipende da alcuni modelli di schede madri e CPU. In alcuni computer, i progettisti hanno posizionato questo chip sulla connessione parallela nord della scheda madre, mentre in altri computer sono posizionati sulla CPU "die". Quei sistemi progettati per installare il controller nella scheda madre hanno un gran numero di nuovi socket fisici diversi. Anche la RAM utilizzata in questo tipo di computer ha un nuovo design moderno.

Lo scopo principale dell'utilizzo di un controller di memoria in un computer è consentire al sistema di leggere e scrivere le modifiche sulla RAM e aggiornarla ad ogni avvio. Ciò è dovuto al fatto che il controller di memoria invia cariche elettriche, che, a loro volta, sono segnali per eseguire determinate azioni. Senza approfondire la terminologia tecnica, possiamo affermare che i controller di memoria sono una delle parti più importanti di un computer che consente l'uso della RAM e senza la quale il suo lavoro sarebbe impossibile.

I controller di memoria sono di diversi tipi. Differiscono in:

- controller di memoria con doppia velocità di trasferimento dati (DDR);

- controller di memoria completamente bufferizzati (FB);

- controller a due canali (DC).

Le funzioni che diversi tipi di controller di memoria possono eseguire differiscono l'una dall'altra. Ad esempio, i controller di memoria a doppia velocità di trasmissione vengono utilizzati per trasferire i dati, a seconda dell'aumento o della diminuzione della frequenza di clock della memoria. Mentre la memoria a doppio canale utilizza due controller di memoria paralleli tra loro. Ciò consente al computer di aumentare la velocità del sistema creando più canali, ma nonostante le difficoltà derivanti dall'utilizzo di un mucchio di cavi, questo sistema funziona in modo abbastanza efficiente. Tuttavia, ci sono difficoltà durante la creazione di nuovi canali, quindi questo tipo di controller di memoria non è perfetto.

I controller di memoria completamente bufferizzati, d'altra parte, sono diversi dagli altri tipi di controller di memoria. Questa tecnologia utilizza i canali di dati seriali necessari per comunicare con la scheda madre e, a differenza di altri sistemi, i circuiti di memoria RAM. Il vantaggio di questo tipo di controller è che i controller di memoria completamente bufferizzati riducono il numero di cavi utilizzati nella scheda madre e quindi riducono il tempo dedicato all'attività.

Come hai già visto, i controller di memoria sono molto necessari per il funzionamento stabile del computer e diversi tipi vengono utilizzati per scopi diversi. I prezzi per le linee di memoria vanno da molto alti a molto bassi, a seconda del tipo e delle funzioni eseguite da un particolare controller di memoria.

Tipicamente, un controller industriale è costituito da: un processore centrale, interfacce di rete, moduli di memoria e vari dispositivi I/O.

Il modulo processore PLC comprende i seguenti componenti: microprocessore o CPU (unità di elaborazione centrale), orologio in tempo reale, dispositivi di memoria e watchdog.

Le caratteristiche principali del microprocessore includono: frequenza di clock, profondità di bit, supporto per porte per vari dispositivi I/O, architettura, parametri prestazionali per determinati intervalli di temperatura, operazioni in virgola mobile, livello di consumo energetico.

Le prestazioni dei microprocessori con la stessa architettura sono proporzionali alla velocità di clock. La maggior parte dei controller utilizza microprocessori implementati sull'architettura RISC (Reduced Instruction Set Computing), che hanno un numero ridotto di istruzioni. In questo caso, il microprocessore utilizza un certo numero di istruzioni che hanno la stessa lunghezza e molti registri. Grazie a un set ridotto di istruzioni, è possibile creare compilatori con indicatori ad alta efficienza, nonché una pipeline di processori in grado di produrre il risultato dell'esecuzione delle azioni di una delle istruzioni in un ciclo.

I controller industriali ad alta intensità di matematica richiedono un coprocessore matematico (un processore ausiliario che esegue operazioni in virgola mobile) o l'uso di processori di segnale che eseguono operazioni matematiche per un ciclo di clock. Grazie ai processori di segnale, si ottiene una significativa accelerazione della convoluzione o delle veloci operazioni di trasformata di Fourier.

La capacità di memoria è caratterizzata dal numero di variabili che possono essere elaborate durante il funzionamento del PLC. Il tempo di accesso alla memoria del microprocessore è uno degli indicatori più significativi che può limitare le prestazioni. Per questo motivo, la memoria è suddivisa in livelli gerarchici, tenendo conto della frequenza e della velocità di utilizzo dei dati in essa disponibili.La gerarchia della memoria è un altro indicatore significativo dell'architettura del processore che consente di ridurre il livello di possibile impatto negativo di memoria lenta sulla velocità del microprocessore.

I principali tipi di memoria per controllori industriali (PLC):

- ROM - Memoria di sola lettura;

- RAM - memoria ad accesso casuale;

- Registro impostato.

Un insieme di registri sono gli elementi di memoria più veloci, poiché vengono utilizzati dall'ALU (unità logica aritmetica) per eseguire le istruzioni più semplici del processore. La ROM viene utilizzata come luogo in cui archiviare informazioni che cambiano raramente: il sistema operativo, il bootloader, i driver di dispositivo o il modulo eseguibile di un programma. La RAM memorizza direttamente i dati soggetti a molteplici modifiche durante il funzionamento del controller. Ad esempio, informazioni sulla diagnostica, variabili visualizzate sul display, valori di tag, calcoli intermedi, dati visualizzati su grafici. Il ruolo della ROM (ROM - Read Only Memory), di regola, è la memoria riprogrammabile elettricamente cancellabile (EEPROM - Electrically Erasable Programmable ROM). A proposito, la memoria flash è essenzialmente una specie di EEPROM. Il suo principio di funzionamento è immagazzinare una certa carica in un condensatore, che è formato dal substrato del MOSFET e dal gate flottante. La caratteristica principale della memoria flash è la sua assoluta non volatilità, ovvero la possibilità di salvare i dati in assenza di alimentazione. L'aggiornamento dei dati nella memoria flash non avviene nelle singole celle, ma attraverso l'utilizzo di blocchi di grandi dimensioni. Tutte le ROM hanno un grosso svantaggio: un basso livello di prestazioni.

Il numero di cicli di immissione delle informazioni nella memoria flash è limitato a poche decine di migliaia di volte. I moderni microprocessori utilizzano la memoria statica (SRAM - Static Random Access Memory), la memoria dinamica (DRAM - Dynamic Random Access Memory) e la memoria dinamica sincrona (SDRAM - Synchronous DRAM) come RAM. L'esecuzione della SRAM avviene su flip-flop in grado di memorizzare informazioni indefinitamente, a condizione che sia disponibile alimentazione. La memoria dinamica di un controllore industriale memorizza i suoi dati sui condensatori, il che richiede la periodica ricarica dei condensatori. Lo svantaggio principale della memoria trigger è l'alto livello di costo e il rapporto prezzo-capacità. Ciò è dovuto al fatto che un numero relativamente piccolo di infradito può essere posizionato su un chip. I vantaggi includono un alto livello di prestazioni, calcolato in gigahertz, mentre la memoria del condensatore non può superare la barra di diverse centinaia di hertz. Tutti i tipi di RAM differiscono in quanto in assenza di alimentazione, tutte le informazioni disponibili in esse non vengono memorizzate. Questo è il motivo per cui alcuni tipi di PLC utilizzano l'alimentazione a batteria per mantenere il sistema in funzione in caso di breve interruzione dell'alimentazione del sistema.

I controller industriali modulari e monoblocco utilizzano un bus parallelo per comunicare con i moduli I/O, ottenendo prestazioni di polling significativamente più veloci rispetto a un bus seriale. Tipi di bus paralleli: VME, PCI, ISA, CXM, ComactPCI, PC/104. È necessario un bus seriale, come RS-485, per collegare i moduli I/O remoti.