Исследование работы логических элементов. Исследование логических элементов ттл, эсл, моп. Аксиомы алгебры логики

Для описания алгоритма работы логических схем используется математический аппарат алгебры логики. Алгебра логики оперирует двумя понятиями: событие истинно (логическая "1") или событие ложно (логический "0"). События в алгебре логики могут быть связаны двумя операциями: сложения (дизъюнкции), обозначаемой знаком U или +, и умножения (конъюнкции), обозначаемой знаком & или точкой. Отношение эквивалентности обозначается знаком =, а отрицание – чертой или апострофом (") над соответствующим символом.

Логическая схема имеет n входов, которым соответствуют n входных переменных X 1 , … X n и один или несколько выходов, которым соответствуют выходные переменные Y 1 …. Y m . Входные и выходные переменные могут принимать два значения X i = 1 или X i = 0.

Переключающая функция (ПФ) логической схемы связывает при помощи логических операций входные переменные и одну из выходных переменных. Число ПФ равно числу выходных переменных, при этом ПФ может принимать значения 0 или 1.

Логические операции . Наибольший практический интерес представляют следующие элементарные операции (функции).

Логическое умножение (конъюнкция),

Логическое сложение (дизъюнкция),

Логическое умножение с инверсией,

Логическое сложение с инверсией,

Суммирование по модулю 2,

Равнозначность.

Логические элементы . Существуют цифровые интегральные микросхемы, соответствующие основным логическим операциям. Логическому умножению соответствует логический элемент "И". Логическому сложению соответствует логический элемент "ИЛИ". Логическому умножению с инверсией - логический элемент "И-НЕ". Логическому сложению с инверсией – логический элемент "ИЛИ-НЕ". Операции инверсии соответствует логический элемент "НЕ". Существуют микросхемы, реализующие и многие другие логические операции.

Таблицы истинности . Основным способом задания ПФ является составление таблицы истинности, в которой для каждого набора входных переменных указывается значение ПФ (0 или 1). Таблица истинности для логического элемента "НЕ" (логическая операция) имеет вид

| Вход Х | Выход Y |

1.1. Исследование характеристик логического элемента "ИЛИ-НЕ"

Схема исследования логического элемента "ИЛИ-НЕ", представлена на рис. 1.

На схеме рис. 1 входы логического элемента "ИЛИ-НЕ" подключены к генератору слов, формирующего последовательность двоичных чисел 00, 01, 10 и 11. Правый (младший) двоичный разряд каждого числа соответствует логической переменной Х1, левый (старший)– логической переменной Х2. К входам логического элемента также подключены логические пробники , которые загораются красным светом при поступлении на этот вход логической "1". Выход логического элемента подключен к логическому пробнику, который загорается красным светом при появлении на выходе логической "1".

Построение схемы исследования логического элемента "ИЛИ-НЕ"

Запустите при помощи ярлыка на рабочем столе Windows программу Electronics Workbench .

Построение схемы рис. 1 произведем в два этапа: сначала разместим как показано на рис. 1 пиктограммы элементов, а затем последовательно соединим их.

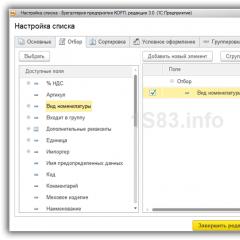

1. Щелкните по кнопке

панели библиотек компонентов и контрольно-измерительных приборов. Из появившегося окна логических элементов вытащите пиктограмму логического элемента NOR ("ИЛИ-НЕ").

2. Щелкните по кнопке

Из появившегося окна последовательно вытащите пиктограммы логических пробников .

3. Разверните логические пробники, так как показано на рис. 1. Для этого на панели функций воспользуйтесь кнопкой поворота

4. Щелкните по кнопке

панели библиотек компонентов и контрольно-измерительных приборов. Из появившегося окна индикаторов вытащите пиктограмму генератора слов

5. Расположите методом буксировки пиктограммы элементов так, как показано на рис. 1 и соедините элементы согласно рисунку.

6. Двойным щелчком кнопки мыши откройте лицевую панель генератора слов .

В левой части панели генератора слов отображаются кодовые комбинации в шестнадцатеричном коде, а в нижней части - в двоичном.

7. Заполним окно шестнадцатеричного кода кодовыми комбинациями, начиная с 0 в верхней нулевой ячейке и далее с прибавлением 1 в каждой последующей ячейке. С этой целью щелкните по кнопке , в появившемся окне предустановок включите опцию Up counter и щелкните по кнопке Accept .

8. В окне Frequency установите частоту формирования кодовых комбинаций равной 1 Гц.

Последовательности двоичных чисел 00, 01, 10 и 11 соответствует в шестнадцатеричном коде - 0, 1, 2, 3. Запрограммируем генератор на периодическое формирование указанной последовательности чисел.

9. Наберите в окне Final число0003 ищелкните на кнопкеCycle .

10. Запустите процесс моделирования при помощи выключателя. Наблюдайте, при каких сочетаниях входных сигналов на выходе логического элемента появится "1". Щелкая по кнопке Step , заполните в Отчете таблицу истинности для элемента "ИЛИ-НЕ". Остановите процесс моделирования при помощи выключателя.

11. Сохраните файл в папке с вашей Фамилией под именем Zan_17_01 .

1. Цель работы

Целью работы является:

Теоретическое изучение логических элементов, реализующих элементарные функции алгебры логики (ФАЛ);

Экспериментальное исследование логических элементов, построенных на отечественных микросхемах серии К155.

2. Основные теоретические положения.

2.1. Математической основой цифровой электроники и вычислительной техники является алгебра логики или булева алгебра (по имени английского математика Джона Буля).

В булевой алгебре независимые переменные или аргументы (X) принимают только два значения: 0 или 1. Зависимые переменные или функции (Y) также могут принимать только одно из двух значений: 0 или 1. Функция алгебры логики (ФАЛ) представляется в виде:

Y = F (X 1 ; X 2 ; X 3 ... X N).

Данная форма задания ФАЛ называется алгебраической.

2.2. Основными логическими функциями являются:

Логическое отрицание (инверсия)

Логическое сложение (дизьюнкция)

Y = X 1 + X 2 или Y = X 1 V X 2 ;

Логическое умножение (коньюнкция)

Y = X 1 · X 2 или Y = X 1 L X 2 .

К более сложным функциям алгебры логики относятся:

Функция равнозначности (эквивалентности)

Y = X 1 · X 2 + или Y = X 1 ~ X 2 ;

Функция неравнозначности (сложение по модулю два)

Y = X 1 · + · X 2 или Y = X 1 X 2 ;

Функция Пирса (логическое сложение с отрицанием)

Функция Шеффера (логическое умножение с отрицанием)

2.3. Для булевой алгебры справедливы следующие законы и правила:

Распределительный закон

X 1 (X 2 + X 3) = X 1 · X 2 + X 1 · X 3 ,

X 1 + X 2 · X 3 = (X 1 + X 2) (X 1 + X 3) ;

Правило повторения

X · X = X , X + X = X ;

Правило отрицания

X · = 0 , X + = 1 ;

Теорема де Моргана

Тождества

X · 1 = X , X + 0 = X , X · 0 = 0 , X + 1 = 1.

2.4. Схемы, реализующие логические функции, называются логическими элементами. Основные логические элементы имеют, как правило, один выход (Y) и несколько входов, число которых равно числу аргументов (X 1 ;X 2 ;X 3 ... X N). На электрических схемах логические элементы обозначаются в виде прямоугольников с выводами для входных (слева) и выходных (справа) переменных. Внутри прямоугольника изображается символ, указывающий функциональное назначение элемента.

На рис.1 ¸ 10 представлены логические элементы, реализующие рассмотренные в п.2.2. функции. Там же представлены так называемые таблицы состояний или таблицы истинности, описывающие соответствующие логические функции в двоичном коде в виде состояний входных и выходных переменных. Таблица истинности является также табличным способом задания ФАЛ.

На рис.1 представлен элемент “НЕ”, реализующий функцию логического отрицания Y = .

Элемент “ИЛИ” (рис.2) и элемент “И” (рис.3) реализуют функции логического сложения и логического умножения соответственно.

Функции Пирса и функции Шеффера реализуются с помощью элементов “ИЛИ-НЕ” и “И-НЕ”, представленных на рис.4 и рис. 5 соответственно.

Элемент Пирса можно представить в виде последовательного соединения элемента “ИЛИ” и элемента “НЕ” (рис.6), а элемент Шеффера - в виде последовательного соединения элемента “И” и элемента “НЕ” (рис.7).

На рис.8 и рис.9 представлены элементы “Исключающее ИЛИ” и “Исключающее ИЛИ - НЕ”, реализующие функции неравнозначности и неравнозначности с отрицанием соответственно.

2.5. Логические элементы, реализующие операции коньюнкции, дизьюнкции, функции Пирса и Шеффера, могут быть, в общем случае, n - входовые. Так, например, логический элемент с тремя входами, реализующий функцию Пирса, имеет вид, представленный на рис.10.

В таблице истинности (рис.10) в отличие от таблиц в п.2.4. имеется восемь значений выходной переменной Y. Это количество определяется числом возможных комбинаций входных переменных N, которое, в общем случае, равно: N = 2 n , где n - число входных переменных.

2.6. Логические элементы используются для построения интегральных микросхем, выполняющих различные логические и арифметические операции и имеющих различное функциональное назначение. Микросхемы типа К155ЛН1 и К155ЛА3, например, имеют в своем составе шесть инверторов и четыре элемента Шеффера соответственно (рис.11), а микросхема К155ЛР1 содержит элементы разного вида (рис.12).

2.7. ФАЛ любой сложности можно реализовать с помощью указанных логических элементов. В качестве примера рассмотрим ФАЛ, заданную в алгебраической форме, в виде:

Упростим данную ФАЛ, используя вышеприведенные правила. Получим:

(2)

(2)

Проведенная операция носит название минимизации ФАЛ и служит для облегчения процедуры построения функциональной схемы соответствующего цифрового устройства.

Функциональная схема утройства, реализующая рассматриваемую ФАЛ, представлена на рис.13.

Следует отметить, что полученная после преобразований функция (2) не является полностью минимизированной. Полная минимизация функции проводится в процессе выполнения лабораторной работы.

3. Описание обьекта и средств исследования

Исследуемое в лабораторной работе устройство представлено на рис.14.

3.1. Устройство представляет собой группу логических элементов, выполненных на микросхемах серии К155 (элементы ДД1¸ДД4).

Для микросхем данной серии логической единице соответствует напряжение U 1 = (2,4 ¸ 5,0) B, а логическому нулю - U 0 = (0 ¸ 0,8) В.

3.2. Логические “0” и “1” на входе элементов задаются с помощью кнопок, расположенных на передней панели блока К32 под надписью “Программатор кодов”. Номера кнопок на панели соответствуют номерам на схеме устройства.

Полное графическое изображение кнопок данного типа (так называемых “кнопок с фиксацией”) показано только для кнопки SA1.

При нажатой кнопке вход элементов через резистор R1 подключается к источнику с напряжением 5В. При этом на входе элементов будет действовать напряжение U 1 , что соотвествует подаче на вывод микросхемы логической единицы. При отжатой кнопке вход элемента будет соединен с шиной, находящейся под потенциалом земли, что соответствует подаче на вывод микросхемы логического нуля U 0 .

3.3. Логические сигналы с выводов элементов ДД1 ¸ ДД4 поступают на цифровые индикаторы и индуцируются в виде символов “0” и “1”. Цифровые индикаторы расположены в блоке К32 слева (кнопка “IO 2”) под индикаторами должна находиться в нажатом состоянии.

3.4. Сигнал с выхода элемента ДД5 через цепи коммутации подается на вход мультиметра Н3014. Предварительно мультиметр устанавливается в режим измерения постоянного напряжения “-V” и выпорлняются следующие подсоединения:

3.4.1. Вход - гнездо мультиметра “-V” - кабелем соединяется с гнездом “Выход V ~“ блока К32.

3.4.2. Гнездо XS1 на плате устройства проводником соединяется с левым гнездом под надписью “Вход 1” в поле надписи “Коммутатор”.

3.4.3. Кнопка “ВСВ ВНК” над указанным выше гнездом должна находиться в нажатом состоянии.

3.4.4. Кнопка “ВХ 1” под надписью “Контроль V ~“ должна находиться в нажатом, а кнопка “ВСВ ВНК” в поле надписи “КВУ” - в отжатом состоянии.

4.1. Исследование особенностей функционирования логических элементов ДД1 ¸ ДД4 и определение их функционального назначения.

4.1.1. Задавая различные комбинации входных логических сигналов, определить значение выходного сигнала и по результатам измерений заполнить таблицы истинности для каждого элемента ДД1 ¸ ДД4 (таблица 1 или таблица 2 соответственно) в лабораторном отчете.

Таблица 1.

Таблица 2.

4.1.2. По результатам измерений (п.4.1.1.) определить функциональное назначение элементов и проставить их обозначение на схеме в лабораторном отчете.

Внимание! Вноситьт обозначения в текст методических указаний категорически запрещается.

4.2. Исследование особенностей функционирования элемента ДД5, определение его функционального гназначения и измерение уровней напряжения, соответсствующих логическим сигналам “0” и “1”.

4.2.1. Задавая с помощью кнопки SA12 лоргические сигналы “0” и “1”, на входе элемента ДД5 по соотношению выходных сигналов определить его функциональное назначение (см.п.3.1.). Провести измерения величины напряжения на выходе элемента для каждой комбинации входных сигналов с помощью мультиметра (п.3.4.). Данные измерений занести в таблицу.

Таблица 3.

4.2.2. По результатам измерений (п.4.2.1.) определить уровни напряжений логического нуля U 0 и логической единицы U 1 для данного типа микросхем и установить их соответствие паспортным данным.

4.3. Провести полную минимизацию ФАЛ, представленной в п.2.7. По результатам минимизации составить функциональную схему устройства.

1. Название и цель работы

2. Схема исследуемого устройства

3. Таблицы 1,2,3

4. Результаты измерений U 0 и U 1 (п.4.2.2.)

5. Формулы для расчета и расчет по п.4.3., схема устройства

6. Выводы по работе

6. Контрольные вопросы

1. Какими значениями переменных оперирует алгебра логики?

2. Основные формы задания ФАЛ

3. Вид основных логических функций в алгебраической форме

4. Что такое “логический элемент”?

5. Какие логические функции выполняют элементы Пирса и Шеффера?

6. Чем определяется число возможных комбинаций входных переменных для произвольного логического элемента?

7. Список использованной литературы

Электротехника и основы электроники. О.А.Антонова, О.П.Глудкин и др., Под ред. проф. О.П.Глудкина.-М.:Высшая школа, 1993.

СЕРГИЕВ ПОСАД

Лабораторная работа № 1

Логические функции, ЭЛЕМЕНТЫ и схемы

Цель работы

Исследование логических функций, логических элементов и схем.

Приборы и элементы

Логический преобразователь.

Генератор слов.

Вольтметр.

Логические пробники.

Источник напряжения + 5 В.

Источник сигнала "логической единицы".

Двухпозиционные переключатели.

Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Микросхемы серии 74.

Краткие сведения из теории

Аксиомы алгебры логики

Переменные, рассматриваемые в алгебре логики, могут принимать только два значения - 0 или 1. В алгебре логики определены отношение эквивалентности (обозначается знаком =), операции сложения (дизъюнкции), обозначаемая знаком , умножения (конъюнкции), обозначаемая знаками &, или точкой, и отрицания (или инверсии), обозначаемая надчеркиванием или апострофом ".

Алгебра логики определяется следующей системой аксиом:

x = 1, если x 0; x = 0, если x 1;

0&0 = 0; 1 1 = 1

1&1 = 1; 0 0 =0;

1&0 = 0&1 = 0; 0 1 = 1 0 = 1;

Логические выражения

Запись логических выражений обычно осуществляют в конъюнктивной или дизъюнктивной нормальных формах. В дизъюнктивной форме логические выражения записываются как логическая сумма логических произведений, в конъюнктивной форме – как логическое произведение логических сумм. Порядок действий такой же, как и в обычных алгебраических выражениях. Логические выражения связывают значение логической функции со значениями логических переменных.

Логические законы и тождества

При преобразованиях логических выражений используются следующие логические законы и тождества

Логические функции

Любое логическое выражение, составленное из n переменных с помощью конечного числа операций алгебры логики, можно рассматривать как некоторую функцию n переменных. Такую функцию называют логической. В соответствии с аксиомами алгебры логики функция может принимать в зависимости от значения переменных значение 0 или 1. Функция n логических переменных может быть определена для 2 n значений переменных, соответствующих всем возможным значениям n-разрядных двоичных чисел Основной интерес представляют следующие функции двух переменных х и у

f 1 (x,y) = x & y = x y = x – логическое умножение (конъюнкция),

f 2 (x,y) = x y – логическое сложение (дизъюнкция),

f 3 (x,y) = = – штрих Шеффера,

f 4 (x,y) = = – стрелка Пирса,

f 5 (x,y) = x y = – сложение по модулю 2,

f 6 (x,y) = ![]() – равнозначность.

– равнозначность.

Логические схемы

Физическое устройство, реализующее одну из операций алгебры логики или простейшую логическую функцию, называется логическим элементом. Схема, составленная из конечного числа логических элементов по определенным правилам, называется логической схемой. Основным логическим функциям соответствуют выполняющие их схемные элементы.

Таблица истинности

Так как область определения любой функции n переменных конечна (2 n значений), такая функция может быть задана таблицей значений f(i), которые она принимает в точках i, где i= 0,…,2 n -1. Такие таблицы называют таблицами истинности. В таблице 1 представлены таблицы истинности, задающие указанные выше функции.

Таблица 1

| Значения переменных | ||||||||

| x | у | f 1 | f 2 | f 3 | f 4 | f 5 | f 6 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 2 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 3 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

Карты Карно

Если число логических переменных не превышает 5-6, преобразования логических уравнений удобно производить с помощью карт Карно. Цель преобразований - получение компактного логического выражения (минимизация). Минимизацию производят объединением соседних наборов (термов). Объединяемые наборы должны иметь одинаковые значения функции (все 0 или все 1). Для наглядности рассмотрим пример: пусть требуется найти логическое выражение для мажоритарной функции f m трех переменных x, у, z, описываемой таблицей истинности, показанной в Таблице 2.

Таблица 2

Мажоритарная функция

| № | x | y | z | f m |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 |

| 6 | 1 | 1 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 |

Здесь номер строки равен числу i= 2 2 x+2 1 y+2 0 z, образованному значениями переменных.

Составим карту Карно. Она представляет собой нечто похожее на таблицу, в которой наименования столбцов и строк представляют собой значения переменных, причем переменные располагаются в таком порядке, чтобы при переходе к соседнему столбцу или строке изменялось значение только одной переменной. Например, в строке xy таблицы 3 значения переменных xy могут быть представлены следующими последовательностями 00,01,11,10 или 00,10,11,01. Таблицу заполняют значениями функции, соответствующими комбинациям значений переменных. Полученная таким образом таблица выглядит, как показано ниже (таблица 3).

Таблица 3

Карта Карно

мажоритарной функции

xy  z z

| 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 |

На карте Карно отмечаем группы, состоящие из 2 k соседних ячеек (2,4,8,) и содержащие 1, так как они описываются простыми логическими выражениями. Три овала в таблице определяют логические выражения xy, xz, yz. Каждый овал, объединяющий две ячейки, соответствует логическим преобразованиям:

Компактное выражение, описывающее функцию, представляет собой дизъюнкцию полученных при помощи карт Карно логических выражений. В результате получаем выражение в дизъюнктивной нормальной форме

f m = xy v xz v yz .

Если объединять 0, то получим выражение в конъюнктивной нормальной форме

f m = (x v y)(x v z)(y v z).

При реализации мажоритарной функции трех логических переменных получим схему, которая при подаче на ее входы трех сигналов сформирует на выходе сигнал, равный сигналу на большинстве входов (2 из 3 или 3 из 3). Эта схема применяется для восстановления истинного значения сигналов, поступающих на 3 входа, если возможна ошибка на одном из входов.

Для реализации этой функции на элементах 2И-НЕ необходимо провести следующие преобразования:

Для ДНФ получилось более простое выражение, поэтому его и следует реализовать. Соответствующая схемная реализация приведена на рис. 1.

|

Рис. 1

ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Транскрипт

1 16 Исследование логики работы логических элементов Цель работы Ц елью работы является закрепление знаний основ алгебры логики и получение навыков в исследовании логических элементов и соединении их в простейшие комбинационные схемы.

2 17 к 1. Сведения из теории омбинационные схемы состоят из логических элементов. Логическим элементом называется простейшая часть цифровой схемы, которая выполняет логические операции над логическими переменными. При использовании интегральных микросхем такими элементами обычно являются элементы типа И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ. Работа логических элементов описывается таблицами истинности. На электрических функциональных схемах логические элементы отображаются в виде условных графических обозначений (УГО). Условные графические обозначения логических элементов на два входа приведены на рис 2.1а 2.1д. Таблицы истинности для этих элементов имеют вид, показанный в табл НЕ 2И 2ИЛИ 2И-НЕ 1 1 а) б) в) г) д) Рис Условные графические обозначения логических элементов Таблица 2.1 Таблица истинности логических элементов В х о д ы Т и п э л е м е н т а a b НЕ 2И 2ИЛИ 2И-НЕ 2ИЛИ-НЕ У = а У = аb У = a v b Y = ab Y = a v b Для записи логической функции в СДНФ (совершенная дизъюнктивная нормальная форма) по таблице истинности необходимо для каждой строки таблицы, в которой функция У принимает значение «1», записать логическое произведение (конъюнкцию) входных переменных (для табл. 2.1 имеются в виду переменные a и b). При этом если переменная в данной строке принимает значение «0», то в конъюнкции она записывается с инверсией. Далее при необходимости следует минимизировать полученную функцию.

3 18 2. Краткое описание лабораторной установки В качестве лабораторной установки используется стенд типа УМ-11. Основу стенда составляют блок питания, генераторы синхроимпульсов и одиночных импульсов, набор логических элементов и триггеров, а также элементы индикации и управления. Входы и выходы всех элементов выведены на переднюю панель стенда в виде контактных гнезд. На передней панели стенда имеются условные графические обозначения логических элементов и триггеров. С помощью специальных проводов с наконечниками можно соединять элементы друг с другом, подавать на входы элементов сигналы от генераторов или с переключателей, а также наблюдать значения сигналов с помощью индикаторных лампочек или с помощью осциллографа. Фрагмент передней панели стенда показан на рис Рис Фрагмент панели стенда УМ-11 Кроме элементов на 2, 3 и 4 входа, показанных на рис. 2.2, на передней панели имеется также элемент И-НЕ на 8 входов. Такой набор элементов соответствует серии 155 интегральных микросхем. Таким образом, с помощью стенда можно собирать комбинационные схемы и проверять правильность их работы.

4 19 3. Порядок выполнения работы Задание 1. Исследовать логику работы элемента 2И-НЕ. Для этого собрать на стенде схему, приведенную на рис При построении схемы использовать переключатели, с помощью которых на вход элемента можно подавать сигналы «0» и «1». сигналы на выходе наблюдать по состоянию индикаторной лампочки. При сборке схемы следует обратить внимание на то, что каждый переключатель может задавать значение одной переменной. При этом переключатель имеет два выхода: прямой (верхний) и инверсный (нижний). Так что с верхнего выхода переключателя можно получить прямое значение переменной, а с нижнего инверсное значение (рис. 2.3). Само прямое значение переменной зависит от положения переключателя: в верхнем положении переключателя переменная равна «1», в нижнем «0». Соответственно инверсное значение будет обратным. С помощью переключателей подать на вход схемы все комбинации сигналов «а» и «b»,» и занести полученные значения выходных сигналов в таблицу истинности. Сравнить полученную таблицу с данными табл. 2.1.для элемента 2И-НЕ. В отчет занести: собранную схему, УГО элемента 2И-НЕ и полученную таблицу истинности. +5V a 1 a b Y 1 b Рис Схема для исследования элемента 2И-НЕ Задание 2. Исследовать логику работы элемента 3И-НЕ. Для этого собрать схему, аналогичную схеме рис Проверить логику работы схемы при различных значениях входных сигналов и составить таблицу истинности. Задание 3. Исследовать логику работы элемента НЕ, реализованного на основе элемента 2И-НЕ. Для этого собрать схему, приведенную на рис. 2.4,. и дополнить ее переключателем и индикаторной лампочкой. Рис Реализация схемы НЕ на элементах 2И-НЕ

5 20 Проверить логику работы схемы при различных значениях входного сигнала и сравнить ее с данными табл. 2.1 для элемента НЕ. Задание 4. Собрать схему, приведенную на рис. 2.5, и исследовать логику ее работы. Составить таблицу истинности и сравнить ее с данными табл. 2.1 для элемента 2И. Рис Схема реализации схемы И на элементах И-НЕ Задание 5. Собрать схему, приведенную на рис.2.6, и исследовать логику ее работы. Составить таблицу истинности и сравнить ее с данными табл. 2.1 для элемента 2ИЛИ. Рис Схема реализации схемы ИЛИ на элементах И-НЕ Задание 6. Собрать схему, приведенную на рис. 2.7, и исследовать логику ее работы. Составить таблицу истинности и сравнить ее с таблицей истинности для элемента 2И-2ИЛИ. Рис Пример схемы на элементах И-НЕ 4. Содержание отчета 1. Тема, цель работы, 2. Результаты выполнения заданий. По каждому заданию привести схему эксперимента, УГО исследуемого элемента и таблицу истинности. 3. Анализ полученных результатов. 4. Выводы по работе.

6 21 5. Контрольные вопросы 1. Что такое логическая функция? 2. Что такое логический элемент? 3. Поясните логику работы элемента НЕ. 4. Поясните логику работы элемента И. 5. Поясните логику работы элемента ИЛИ. 6. Поясните логику работы элемента И-НЕ. 7. Поясните логику работы элемента ИЛИ-НЕ. 8. Что такое таблица истинности? 9. Как по таблице истинности записать логическую функцию в СДНФ? 10. Как из элементов И-НЕ построить схему НЕ? 11. Как из элементов И-НЕ построить схему И? 12. Как из элементов И-НЕ построить схему ИЛИ? 13. Какую функцию реализует схема, приведенная на рис. 2.7.

23 1. Общие сведения о комбинационных схемах Комбинационные схемы состоят из логических элементов. При использовании интегральных микросхем такими элементами обычно являются элементы типа И-НЕ, ИЛИ-НЕ,

Лабораторная работа 8 Моделирование простейших логических схем Цель работы моделирование логических функций при помощи логических элементов. Рабочее задание Домашнее задание. В соответствии с заданным

Назначение программы 34 1. Краткое описание программы Программа Electronics Workbench предназначена для моделирования электронных схем (аналоговых и цифровых) и позволяет изображать схемы на экране и моделировать

Министерство образования и науки Российской Федерации Уральский федеральный университет имени первого Президента России Б. Н. Ельцина ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ НА ИНТЕГРАЛЬНЫХ МИКРОСХЕМАХ Методические указания

Лабораторная работа 10 Моделирование триггеров и регистров Цель работы приобретение практических навыков построения и исследования различных типов триггеров и регистров. Рабочее задание 1 Домашнее задание

Работа 8. Исследование мультиплексоров Цель работы: изучение принципов построения, практического применения и экспериментального исследования мультиплексоров Продолжительность работы 4 часа. Самостоятельная

Практическая работа 1 Анализ и синтез логических и релейных систем управления ВВЕДЕНИЕ Устройства дискретного действия, выполненные на элементах гидро-, пневмо- и электроавтоматики, и управляющие микропроцессоры

Министерство образования и науки и РФ Федеральное автономное образовательное учреждение высшего образования ЮЖНЫЙ ФЕДЕРАЛЬНЫЙ УНИВЕРСИТЕТ Институт нанотехнологий, электроники и приборостроения ЭЛЕКТРОННЫЙ

Название теста: Схемотехника Предназначено для студентов специальности: спец._ис_(2 курс_3_ г.о.) Отделение рус. ОЧНОЕ Текст вопроса 1 Дайте определение понятию символ 2 Дайте определение понятию код

Работа ИССЛЕДОВАНИЕ ДЕШИФРАТОРОВ Цель работы: изучение принципов построения и методов синтеза дешифраторов; макетирование и экспериментальное исследование дешифраторов В процессе самостоятельной подготовки

Работа 1 Исследование работы логических элементов 1. Цель работы Целью работы является исследование принципа действия цифровых логических элементов (ЛЭ). 2. Методические указания 2.1. ЛЭ и операция логического

Федеральное государственное автономное образовательное учреждение высшего образования "Национальный исследовательский университет "Высшая школа экономики" Факультет: Московский институт электроники и математики

Казанский государственный технический университет им. А.Н. Туполева Кафедра радиоэлектронных и телекоммуникационных систем Щербакова Т.Ф., Култынов Ю.И. Комбинационные и последовательные узлы цифровых

Работа. СИНХРОННЫЕ ДВУХСТУПЕНЧАТЫЕ ТРИГГЕРЫ Цель работы изучение принципов построения и схем, статических и динамических режимов работы синхронных двухступенчатых триггеров. Продолжительность работы часа..структура

Лекция 5 Синтез комбинационных схем на дешифраторах Определение и классификация Дешифратором называют комбинационное устройство, которое в общем случае преобразует один тип двоичного кода в другой. Наиболее

ЛАБОРАТОРНАЯ РАБОТА 4 «Исследование работы Шифраторов и Дешифраторов» 1 Цель работы: 1.1 Ознакомление с основными характеристиками интегральных преобразователей кодов: дешифраторов, шифратораторов. 2 Литература:

МИНИСТЕРСТВО ОБРАЗОВАНИЯ РОССИЙСКОЙ ФЕДЕРАЦИИ МОСКОВСКИЙ ЭНЕРГЕТИЧЕСКИЙ ИНСТИТУТ (ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ) А.Т. КОБЯК ТРИГГЕРЫ Методическое пособие к лабораторной работе МОСКВА 2004 ТРИГГЕРЫ Триггером

Методическое пособие для учащихся по информатике Тема 1. Формы представления логических функций (совершенные дизъюнктивные и конъюнктивные нормальные формы) Приложение 2.19.5 Если логическая функция представлена

222 Лабораторная работа 13 Синтез и моделирование работы преобразователя кода 1. Цель работы Освоить порядок синтеза и моделирования преобразователя кода с помощью программы Multisim 11.0.2. 2. Общие сведения

Лабораторная работа 1 Цифровая логика компьютера. 1. Цель работы Целью работы является изучение логических элементов компьютера и их таблиц истинности, а также построение триггеров в программе Logisim.

Исследование логической микросхемы КЛА7 Цель работы изучить устройство и принцип действия логической микросхемы КЛА7. Общие сведения Интегральная схема КЛА7 содержит элемента И-НЕ, построенных на КМОП-структурах.

«ЛОГИКА-М» Учебно-лабораторный стенд Техническое описание и инструкция по эксплуатации Содержание стр. 1. Назначение... 2 2. Технические характеристики... 2 3. Конструкция стенда... 3 4. Лабораторная работа

ЗАДАНИЯ И МЕТОДИЧЕСКИЕ УКАЗАНИЯ по выполнению контрольной работы по дисциплине «Элементы систем автоматики» студентами заочного факультета Направление подготовки 000-Электроэнергетика и электротехника

Решение задач с использованием конъюнктивной нормальной и дизъюнктивной нормальной форм Лапшева Елена Евгеньевна, ПРЦНИТ СГУ, МОУ «Физико-технический лицей г Саратова» 6 февраля 2007 г В задачниках по

Министерство образования и науки Российской Федерации Федеральное агентство по образованию Саратовский Государственный Технический Университет ИССЛЕДОВАНИЕ РЕГИСТРОВ Методические указания к выполнению

3. Элементы схемотехники. Логические схемы Цели: - познакомиться с элементами и принципами построения логических схем; - закрепить понимание основных законов алгебры логики; - учиться упрощать логические

Контрольно-оценочные средства для проведения текущего контроля по МДК.01.01 Цифровая схемотехника (2 курс, семестр 2018-2019 уч. г.) Текущий контроль 1 Форма контроля: Практическая работа (Опрос) Описательная

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА Федеральное Государственное Бюджетное Образовательное Учреждение Высшего Профессионального Образования «МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ПУТЕЙ СООБЩЕНИЯ»

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РФ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ «НИЖЕГОРОДСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ им. Р.Е.

ЛАБОРАТОРНАЯ РАБОТА 1 СИНТЕЗ КОМБИНАЦИОННЫХ УСТРОЙСТВ ПО ЗАДАННОЙ ЛОГИЧЕСКОЙ ФУНКЦИИ Цель работы: 1. Изучение способов синтеза комбинационных устройств по заданной логической функции. 2. Построение комбинационных

Лабораторная работа 9 Моделирование комбинационных устройств Цель работы изучение форм представления чисел в цифровых устройствах и исследование схем комбинационных цифровых устройств дешифраторов, мультиплексоров

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ПО ОБРАЗОВАНИЮ ГОСУДАРСТВЕННОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ «ВОРОНЕЖСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ» ЛОГИЧЕСКИЕ ЭЛЕМЕНТЫ Методические указания

Логические модели переключательных схем Обработка б информации Физический принцип обработки информации подлежащая преобразованию информация кодируется последовательностью импульсов, обработка которых происходит

Работа. Синхронные одноступенчатые триггеры со статическим и динамическим управлением записью Цель работы изучить схемы асинхронного -триггера, который является запоминающей ячейкой всех типов триггеров,

Лабораторная работа 11 Моделирование счетчиков импульсов Цель работы изучение структуры и исследование работы суммирующих и вычитающих двоичных счетчиков, а также счетчиков с коэффициентом пересчета, отличным

Лабораторная работа 2. Триггеры Цель: Изучение назначения и принцип работы устройств триггера. Знакомство с базовыми устройствами триггер из библиотеки EWB. Оборудование: Электронная лаборатория Electronics

ЭЛЕМЕНТЫ СИСТЕМ АВТОМАТИКИ Тема 2 Логические схемы и их минимизация И.В. Музылёва 23 Основные понятия алгебры логики http://cifra.studentmiv.ru Логические схемы Составление таблиц истинности для логических

4. ЛАБОРАТОРНАЯ РАБОТА 3 RS И D-ТРИГГЕРА Цель занятия: построение и ознакомление с работой основных схем RS и D триггеров с помощью инструментальных средств цифровой части пакета EWB, закрепления теоретического

1. ЦЕЛЬ РАБОТЫ 1.1. Изучить функциональные и электрические характеристики АЛУ на ИМС К155 ИП3. 1.2. Получить практические навыки по исследованию работы ИМС АЛУ, путем подачи входных воздействий, наблюдения

1. ЦЕЛЬ РАБОТЫ 1.1. Изучить функциональные и электрические характеристики дешифраторов на ИМС К 155 ИД4; К 155 ИД7; 1.2. Получить практические навыки по исследованию работы ИМС дешифраторов путем подачи

Тема 4. Логические основы ЭВМ 1.ОСНОВНЫЕ СВЕДЕНИЯ ИЗ АЛГЕБРЫ ЛОГИКИ... 1 2. ЗАКОНЫ АЛГЕБРЫ ЛОГИКИ... 4 3. ПОНЯТИЕ О МИНИМИЗАЦИИ ЛОГИЧЕСКИХ ФУНКЦИЙ... 6 4.ТЕХНИЧЕСКАЯ ИНТЕРПРЕТАЦИЯ ЛОГИЧЕСКИХ ФУНКЦИЙ...

Направление 09.03.03 Информатика 1.2 Лекция «Логические основы информатики» Лектор Молнина Елена Владимировна Старший преподаватель кафедры Информационных систем, ауд.9, гл.корпус. mail: [email protected]

ЛАБОРАТОРНАЯ РАБОТА ИЗУЧЕНИЕ ЭЛЕКТРИЧЕСКИХ ПРОЦЕССОВ В ПРОСТЫХ ЛИНЕЙНЫХ ЦЕПЯХ Цель работы: исследование коэффициента передачи и сдвига фаз между силой тока и напряжением в цепях, состоящих из последовательно

Контрольное задание В зависимости от выданного варианта Вам необходимо построить КЛС дешифратора, шифратора, мультиплексора или сумматора. Вариант 7 в десятичное: «7» 7 «7» 7 0 0 0 0 0 0 0 5 0 0 0 0 0

Поправку и у вас есть все шансы научиться разбираться в людях. В результате проведенного исследования было выявлено, что большая часть студентов использует язык жестов и частично понимает значение телодвижений.

3 Лекция 3. КОМБИНАЦИОННЫЕ ЦИФРОВЫЕ УСТРОЙСТВА План. Шифраторы, дешифраторы и преобразователи кодов.. Мультиплексоры и демультиплексоры. 3. Сумматоры.. Выводы.. Шифраторы, дешифраторы и преобразователи

Электроника и МПТ Синтез логических схем по заданной функции Представление логических функций (ЛФ) 3 способа представления логических функций:. графиком (в виде временной диаграммы напряжения); 2. аналитическим

ИССЛЕДОВАНИЕ ЭЛЕМЕНТАРНЫХ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ Методические указания Ульяновск 2006 1 Федеральное агентство по образованию Государственное образовательное учреждение высшего профессионального образования

Министерство образования и науки Российской Федерации Федеральное государственное автономное образовательное учреждение высшего профессионального образования «Казанский (Приволжский) федеральный университет»

ЛАБОРАТОРНАЯ РАБОТА «ОСНОВЫ ЦИФРОВОЙ ТЕХНИКИ» Рис. 1. Общий вид лабораторного стенда 1 Работа 1 ИССЛЕДОВАНИЕ ГЕНЕРАТОРОВ ПРЯМОУГОЛЬНЫХ ИМПУЛЬСОВ 1. Цель работы Ознакомление с основными функциями и тестирование

МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ НАЦІОНАЛЬНА МЕТАЛУРГІЙНА АКАДЕМІЯ УКРАЇНИ МЕТОДИЧНІ ВКАЗІВКИ до виконання лабораторних робіт та практичних занять з дисципліни «АРХІТЕКТУРА КОМП ЮТЕРІВ» для студентів

МИНИСТЕРСТВО ТРАНСПОРТА РФ ГОСУДАРСТВЕННАЯ СЛУЖБА ГРАЖДАНСКОЙ АВИАЦИИ МОСКОВСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ ГРАЖДАНСКОЙ АВИАЦИИ Кафедра вычислительных машин, комплексов, систем и сетей Курсовая

{ основные понятия - составление сложных выражений - таблицы истинности - законы логики высказываний - примеры } Исходным понятием логики высказываний является простое или элементарное высказывание. Это

Лабораторная работа 3 Схемы на D-триггерах Кафедра ВС СибГУТИ 2012 год Содержание 1. Цели работы:... 3 2. Триггер в счётном режиме... 3 3. Делитель... 3 4. Описание микросхем К176ТМ1 и К176ТМ2... 4 5.

АРХИТЕКТУРА ЭВМ И ВЫЧИСЛИТЕЛЬНЫХ СИСТЕМ Лекция 3. Логические основы ЭВМ, элементы и узлы. Преподаватель Цвелой Владимир Андреевич ЦЕЛЬ: ИЗУЧИТЬ ОСНОВНЫЕ ОПЕРАЦИИ АЛГЕБРЫ ЛОГИКИ, ОСНОВЫ ПОСТРОЕНИЯ КОМБИНАЦИОННЫХ

Глава 3 ЛОГИКА И ЛОГИЧЕСКИЕ ОСНОВЫ КОМПЬЮТЕРА 3.1. Алгебра логики Первые учения о формах и способах рассуждений возникли в странах Древнего Востока (Китай, Индия), но в основе современной логики лежат

1 Простейшие преобразователи информации Математическая логика с развитием вычислительных машин оказалась в тесной взаимосвязи с вычислительной математикой, со всеми вопросами конструирования и программирования

1. ЦЕЛЬ РАБОТЫ 1.1. Изучить функциональные и электрические характеристики полупроводниковых ПЗУ на ИМС К155ПР6, К155ПР7. 1.2. Получить практические навыки по исследованию работы ИМС ПЗУ К155ПР6, К155ПР7

Содержание Предисловие 14 Глава 1. Цифровые системы и представление информации 19 1.1. Цифровые системы 19 1.1.1. Управляющие системы 20 Логические сигналы и функции 21 Положительная и отрицательная логика

Министерство образования и науки РФ Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования Нижегородский государственный технический университет им. Р.Е.

А.И.Недашковский Лабораторная работа Асинхронные и синхронные счетчики импульсов Цель работы знание структур построения, параметров и режимов работы счетчиков импульсов, умение анализировать их работу,

Министерство образования Российской Федерации ОРЕНБУРГСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ Кафедра приборостроения Е. А. Корнев МЕТОДИЧЕСКИЕ УКАЗАНИЯ к лабораторным работам по дисциплинам «Вычислительная техника»,

Открытый урок «Построение логических схем. Базовые логические элементы». Тип урока: комбинированный (проверка знаний учащихся, изучение нового материала). Класс: 10 А класс Дата проведения: 17.01.2009г.

Лабораторная работа 2. Исследование работы триггеров. Кафедра ВС СибГУТИ 2012 год Содержание 1. Цель работы:... 3 2. Общие сведения... 3 3. Асинхронный RS-триггер... 4 4. Синхронный одноступенчатый D-триггер....

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ Задание на работу Измерить вибрации при установке машины без амортизаторов и с амортизаторами. По результатам измерений определить эффективность виброизоляции машины. В усложненных

Лабораторная работа №2

Литература:

2. В.С. Ямпольский Основы автоматики и ЭВТ. – М.: Просвещение. - 1991. - §3.1 ‑3.4

Ход работы:

- Включить терминал, подключиться к локальной сети и загрузить сайт «Основы микроэлектроники». Выбрать номер лабораторной работы, зарегистрироваться и приступить к выполнению заданий согласно появляющимся на экране инструкциям и данному описанию.

- В каждом из 10 заданий выделить из приведенной схемы цифрового автомата узел, содержащий только логические элементы, и изобразить его принципиальную схему, используя УГО российского стандарта

- Смоделировать работу каждой схемы средствами Electronic Workbench и составить таблицу истинности исследуемого устройства

- Определить логическую функцию исследуемого устройства и привести его условное графическое изображение (УГО)

- В каждом задании составить дополнительно две схемы реализации той же логической функции на элементах 2И-НЕ (элемент Шеффера) и элементах 2ИЛИ-НЕ (элемент Пирса), используя минимальное количество вентилей

- В задании 11 по аналогии с предыдущими схемами дополнить приведенное устройство схемой узла, позволяющего подавать на входы Х1¸Х3 произвольную комбинацию логических сигналов и индицировать состояние каждого входа и выхода. Исследовать работу схемы аналогично предыдущим заданиям

Отчет к каждому заданию лабораторной работы оформлять по образцу, приведенному в ПРИЛОЖЕНИИ 1.

При защите работы уметь объяснить каждый из полученных результатов.

ПРИЛОЖЕНИЕ 1

Фрагмент отчета (на примере одного задания)

Задание 1.

Пример схемы, приведенной в задании.

В таком виде перерисовывать её не нужно !

Фрагмент отчета по данному заданию приводится ниже.

Задание 1: выполняемая схемой функция ‑ «2И-НЕ»

Схема: УГО: Таблица истинности:

«2И-НЕ» на элементах Шеффера. «2И-НЕ» на элементах Пирса.

ПРИЛОЖЕНИЕ 2

УГО и таблицы истинности некоторых логических элементов

1. Элемент «2И-НЕ»

2. Элемент «2ИЛИ-НЕ»

3. Элемент «исключающее ИЛИ»

ПРИЛОЖЕНИЕ 3

Примеры условных графических обозначений логических элементов по ГОСТ (российский стандарт) и ANSI (American National Standard Institute)

| УГО по ANSI | УГО по ГОСТ | Функциональное назначение |

| «2И» (2-Input AND Gate) | ||

| «3И» (3-Input AND Gate) | ||

| «2И-НЕ» (2-Input NAND Gate) | ||

| «2ИЛИ» (2-Input OR Gate) | ||

| «2ИЛИ-НЕ» (2-Input NOR Gate) | ||

| «3ИЛИ-НЕ» (3-Input NOR Gate) | ||

| «НЕ» (NOT Gate) | ||

| «исключающее ИЛИ» (2-Input XOR Gate) | |

| «исключающее ИЛИ-НЕ» (2-Input XNOR Gate) | ||

| 6-входовый сумматор по модулю 2 (6-Input XOR Gate) |

Лабораторная работа № 3.

Исследование триггеров RS-, RST-, D- и JK-типов.

Литература:

1. А.А. Коваленко, М.Д. Петропавловский. Основы микроэлектроники: Учебное пособие. ‑ Барнаул: Изд‑во БГПУ, 2005. – 222 с.

2. В.С. Ямпольский. Основы автоматики и электронно-вычислительной техники. – М.: Просвещение. – 1991. – 223 с.

4. Руководство к выполнению виртуальных лабораторных работ с помощью программы моделирования электрических схем Electronic Workbench 5.12

Ход работы:

- Включить терминал, подключиться к локальной сети и загрузить сайт «Основы микроэлектроники». Выбрать номер лабораторной работы, зарегистрироваться и приступить к выполнению заданий согласно появляющимся на экране инструкциям и данному описанию

- Исследуйте работу асинхронного RS-триггера с инверсными входами на логических элементах 2И-НЕ.

Пользуясь программой Electronics Workbench, соберите схему триггера, приведенную на рисунке.

Для управления триггером используйте переключатели (Switch), подсоединяющие входы к клемме плюса питания (V cc) либо к клемме земли (Ground), а для индикации состояния входов и выходов – пробники (соответственно Green Probe и Red Probe).

Исследование провести в следующем порядке:

Таблица состояний триггера

| № комбинации | Операция | ||

| Установка выхода | |||

В сокращенном варианте таблицу состояний RS-триггера с инверсными входами принято изображать в следующем виде (при данной комбинации входных сигналов выход Q устанавливается в указанное состояние независимо от его предыдущего состояния):

Здесьсимвол (t+1) означает состояние триггера «в следующем такте», т.е. после установления выхода в соответствии со входными сигналами

Здесьсимвол (t+1) означает состояние триггера «в следующем такте», т.е. после установления выхода в соответствии со входными сигналами

Примечание: (в этой и других подобных таблицах приняты следующие обозначения ):

- Исследуйте работу асинхронного RS-триггера с прямыми входами на логических элементах 2И-НЕ.

Для этого добавьте к собранной схеме еще 2 элемента 2И-НЕ, чтобы получить триггер с прямыми входами (см. рисунок), и на основе эксперимента в среде Electronics Workbench по аналогии с предыдущим заданием заполните таблицу его состояний

Для этого добавьте к собранной схеме еще 2 элемента 2И-НЕ, чтобы получить триггер с прямыми входами (см. рисунок), и на основе эксперимента в среде Electronics Workbench по аналогии с предыдущим заданием заполните таблицу его состояний

- Исследуйте работу синхронизируемого RS-триггера (RST-триггера).

|

Для этого откройте схему RST-триггера (файл E:\MeLabs\Lab3\rst_trig_analis.EWB), ко входам которого подключен генератор слова (Word Generator), а все входные и выходные сигналы контролируются логическим анализатором (Logic Analyzer). Разверните панель генератора слова и установите для него режим пошаговой работы (Step). Введите в память генератора 16-ричные коды слов Вашего варианта. Разверните панель логического анализатора. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Зарисуйте в тетрадь полученные логическим анализатором диаграммы. Заполните потактовую таблицу состояний триггера.

Таблица состояний триггера

| Информац. сигнал | Номера тактов | |||||||||

| C | ||||||||||

| R | ||||||||||

| S | ||||||||||

| Q |

- Исследуйте работу статического и динамического D‑триггеров. Откройте схему параллельно включенных статического и динамического D‑триггеров (файл E:\MeLabs\Lab3\D_trig.EWB), ко входам которых подключен генератор слова (Word Generator), а все входные и выходные сигналы контролируются пробниками.

|

Разверните панель генератора слова. Из таблицы состояний выпишите по тактам двоичные коды слов и, преобразовав их в 16-ные, введите в память генератора слов. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Заполните потактовую таблицу состояний триггеров.

Таблица состояний триггеров

| Информац. сигнал | Номера тактов | |||||||||

| C | ||||||||||

| D | ||||||||||

| Q стат. | ||||||||||

| Q дин. |

- Откройте схему JK-триггера с динамическим управлением (jk_триг_анализ).

|

Разверните панель генератора слова и установите для него режим пошаговой работы (Step). Введите в память генератора 16-ричные коды слов Вашего варианта. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Зарисуйте в тетрадь полученные логическим анализатором диаграммы. Заполните потактовую таблицу состояний триггера.

Таблица состояний триггера

| Информац. сигнал | Номера тактов | |||||||||||

| C | ||||||||||||

| J | ||||||||||||

| K | ||||||||||||

| Pre | ||||||||||||

| Clr | ||||||||||||

| Q |

Замечание: В отличие от ранее исследовавшихся схем в этом задании исследуется работа конкретной микросхемы 7476 (Dual JK MS‑SLV FF (pre, clr)), в связи с чем при моделировании необходимо к соответствующим выводам подключить источник питания Vcc и заземление GND. В задании задействованы выводы только одного из JK-триггеров (первого). Входы Pre (предустановка) и Clr (очистка) играют роль установочных входов S и R соответственно.

- Выберите из библиотеки Digital интегральную схему JK-триггера 7472 (And‑gated JK MS‑SLV FF (pre, clr)) и соберите на ней схему счетного триггера. Обратите внимание, что на информационных входах используется логика 3И. Вывод NC микросхемы – свободный (не используется).

Подайте на вход триггера однополярные амплитудой 5 В прямоугольные импульсы от функционального генератора требуемой частоты, получите осциллограммы входного и выходного сигналов. Продемонстрируйте их преподавателю.

Подайте на вход триггера однополярные амплитудой 5 В прямоугольные импульсы от функционального генератора требуемой частоты, получите осциллограммы входного и выходного сигналов. Продемонстрируйте их преподавателю.