Исследование логических элементов. Исследование логики работы. логических элементов. Краткие сведения из теории

Для описания алгоритма работы логических схем используется математический аппарат алгебры логики. Алгебра логики оперирует двумя понятиями: событие истинно (логическая "1") или событие ложно (логический "0"). События в алгебре логики могут быть связаны двумя операциями: сложения (дизъюнкции), обозначаемой знаком U или +, и умножения (конъюнкции), обозначаемой знаком & или точкой. Отношение эквивалентности обозначается знаком =, а отрицание – чертой или апострофом (") над соответствующим символом.

Логическая схема имеет n входов, которым соответствуют n входных переменных X 1 , … X n и один или несколько выходов, которым соответствуют выходные переменные Y 1 …. Y m . Входные и выходные переменные могут принимать два значения X i = 1 или X i = 0.

Переключающая функция (ПФ) логической схемы связывает при помощи логических операций входные переменные и одну из выходных переменных. Число ПФ равно числу выходных переменных, при этом ПФ может принимать значения 0 или 1.

Логические операции . Наибольший практический интерес представляют следующие элементарные операции (функции).

Логическое умножение (конъюнкция),

Логическое сложение (дизъюнкция),

Логическое умножение с инверсией,

Логическое сложение с инверсией,

Суммирование по модулю 2,

Равнозначность.

Логические элементы . Существуют цифровые интегральные микросхемы, соответствующие основным логическим операциям. Логическому умножению соответствует логический элемент "И". Логическому сложению соответствует логический элемент "ИЛИ". Логическому умножению с инверсией - логический элемент "И-НЕ". Логическому сложению с инверсией – логический элемент "ИЛИ-НЕ". Операции инверсии соответствует логический элемент "НЕ". Существуют микросхемы, реализующие и многие другие логические операции.

Таблицы истинности . Основным способом задания ПФ является составление таблицы истинности, в которой для каждого набора входных переменных указывается значение ПФ (0 или 1). Таблица истинности для логического элемента "НЕ" (логическая операция) имеет вид

| Вход Х | Выход Y |

1.1. Исследование характеристик логического элемента "ИЛИ-НЕ"

Схема исследования логического элемента "ИЛИ-НЕ", представлена на рис. 1.

На схеме рис. 1 входы логического элемента "ИЛИ-НЕ" подключены к генератору слов, формирующего последовательность двоичных чисел 00, 01, 10 и 11. Правый (младший) двоичный разряд каждого числа соответствует логической переменной Х1, левый (старший)– логической переменной Х2. К входам логического элемента также подключены логические пробники , которые загораются красным светом при поступлении на этот вход логической "1". Выход логического элемента подключен к логическому пробнику, который загорается красным светом при появлении на выходе логической "1".

Построение схемы исследования логического элемента "ИЛИ-НЕ"

Запустите при помощи ярлыка на рабочем столе Windows программу Electronics Workbench .

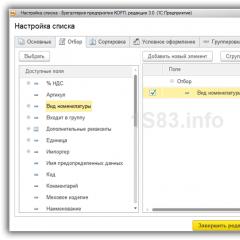

Построение схемы рис. 1 произведем в два этапа: сначала разместим как показано на рис. 1 пиктограммы элементов, а затем последовательно соединим их.

1. Щелкните по кнопке

панели библиотек компонентов и контрольно-измерительных приборов. Из появившегося окна логических элементов вытащите пиктограмму логического элемента NOR ("ИЛИ-НЕ").

2. Щелкните по кнопке

Из появившегося окна последовательно вытащите пиктограммы логических пробников .

3. Разверните логические пробники, так как показано на рис. 1. Для этого на панели функций воспользуйтесь кнопкой поворота

4. Щелкните по кнопке

панели библиотек компонентов и контрольно-измерительных приборов. Из появившегося окна индикаторов вытащите пиктограмму генератора слов

5. Расположите методом буксировки пиктограммы элементов так, как показано на рис. 1 и соедините элементы согласно рисунку.

6. Двойным щелчком кнопки мыши откройте лицевую панель генератора слов .

В левой части панели генератора слов отображаются кодовые комбинации в шестнадцатеричном коде, а в нижней части - в двоичном.

7. Заполним окно шестнадцатеричного кода кодовыми комбинациями, начиная с 0 в верхней нулевой ячейке и далее с прибавлением 1 в каждой последующей ячейке. С этой целью щелкните по кнопке , в появившемся окне предустановок включите опцию Up counter и щелкните по кнопке Accept .

8. В окне Frequency установите частоту формирования кодовых комбинаций равной 1 Гц.

Последовательности двоичных чисел 00, 01, 10 и 11 соответствует в шестнадцатеричном коде - 0, 1, 2, 3. Запрограммируем генератор на периодическое формирование указанной последовательности чисел.

9. Наберите в окне Final число0003 ищелкните на кнопкеCycle .

10. Запустите процесс моделирования при помощи выключателя. Наблюдайте, при каких сочетаниях входных сигналов на выходе логического элемента появится "1". Щелкая по кнопке Step , заполните в Отчете таблицу истинности для элемента "ИЛИ-НЕ". Остановите процесс моделирования при помощи выключателя.

11. Сохраните файл в папке с вашей Фамилией под именем Zan_17_01 .

Данный набор позволяет изучить логику работы основных типов логических элементов. Набор размещается в укладке представляющей собой черный пластиковый ящик размером 200 х 170 х 100 мм

В укладке располагается четыре модуля стандартного размера 155 х 95 х 30 мм. Кроме этого там должны быть соединительные провода, но в экземпляре, с которым имел дело автор, они отсутствовали, но, сохранилось руководство по эксплуатации .

Логический элемент И

Первый модуль это логический элемент И , на его выходе сигнал появляется только при условии того, что сигнал приходит на оба его информационных входа.

Стандартный модуль представляет собой печатную плату, которая сверху закрыта прозрачной пластиковой крышкой, укрепленной на двух винтах.

Модуль легко разбирается, что позволяет подробно рассмотреть печатную плату устройства. С тыльной стороны печатные проводники закрыты непрозрачной пластиковой крышкой.

Логический элемент ИЛИ

Практически аналогично устроен логический элемент ИЛИ , на его выходе сигнал появляется при условии прихода сигнала на любой из его информационных входов.

Логический элемент НЕ

Логический элемент НЕ . Сигналы на входе и выходе этого элемента всегда имеют противоположные значения.

Триггер

Триггер - логическое устройство с двумя устойчивыми состояниями, используется как основа для всевозможных устройств требующих хранения информации.

В целом данный набор по цифровой электроники аналогичен комплекту «Электронный усилитель». Разумеется, представленный в наборе вариант реализации логических элементов далеко не является единственным. По сути, здесь логические элементы реализованы, так как это делалось в 60-е годы XX века. В данном случае важно то, что при работе с данным набором можно непосредственно изучить простейший схемотехнический пример лежащий в самой основе цифровой полупроводниковой электроники. Таким образом, отдельный логический элемент перестает быть «черным ящиком», который работает на чистой магии. Хорошо видимая и одновременно защищенная электрическая схема, это как раз то, что нужно для изучения основ электроники. Автор обзора - Denev.

Транзистор - это компонент из полупроводникового материала, который позволяет управлять достаточно большим электрическим током в цепи за счет изменения тока более малой величины на управляющем электроде.

Существуют биполярные и полевые транзисторы. Различаются они тем, что в биполярном транзисторе перенос зарядов осуществляется как основными, так и неосновными носителями зарядов - дырками и электронами. В полевых транзисторах перенос зарядов осуществляется только одним типом носителей.

Синтез и исследование элементов на транзисторно-транзисторной логике (ТТЛ). Схемы ТТЛ базируются на биполярных транзисторах npn-структуры. Биполярные транзисторы имеют такое название от того, что перенос зарядов в них осуществляется двумя типами носителей - электронами и дырками. Базовым элементом данной технологии является схема И-НЕ. Логическое умножение осуществляется за счет свойств многоэмиттерного транзистора.

Элемент ИЛИ-НЕ.

Реализация логического элемента ИЛИ-НЕ на биполярных транзисторах представлена на рисунке 1.1.

Логическую функцию ИЛИ-НЕ можно выразить функции И и НЕ с помощью правил де Моргана: отрицание дизъюнкции есть конъюнкция отрицаний. На схема имеется два инвертора VT1 и VT2 на которые подаются с помощью ключей и напряжения противоположных полярностей. При подаче логического нуля на оба входа («земля») происходит разряжение в p-области транзистора, он становится закрытым, при этом ток начинает течь через транзисторы VT3, VT4, которые выполняют функцию И, уровень напряжения достаточен для обеспечения логической единицы. Если хотя бы на один вход будет подана логическая единица («плюс»), то произойдёт падение напряжение на одном из выходов инверторов, напряжения на выходе И не будет достаточно для обеспечения логической единицы.

Рисунок 1.1 - Логический элемент ИЛИ-НЕ на биполярных транзисторах

Рисунок 1.2 - на входы элемента ИЛИ-НЕ поданы логические нули

На рисунке 1.2 представлен вариант работы транзисторной схемы, когда на входы поданы логические нули, в результате на выходе будет значение логической единицы.

Элемент ИЛИ-НЕ рождает следующую таблицу истинности (см. таб. 1.1):

Таблица 1.1 - Таблица истинности элемента ИЛИ-НЕ

Элемент НЕ.

Элемент НЕ на ТТЛ представлен на рисунке 1.3.

Рисунок 1.3 - Логический инвертор (логическая функция НЕ)

При установке переключателя на сторону «плюса», течёт малый эмиттерный ток, этот ток позволяет открыть транзистор, происходит падение напряжения и индикатор не загорается, что соответствует логическому нулю. При установке ключа на сторону «земли», происходит расширение закупоривающего слоя, сопротивление транзистора становится много больше сопротивления резистора, транзистор закрыт, падения напряжения не происходит, что соответствует логической единице.

Таблица истинности элемента НЕ (см. таб. 1.2).

Таблица 1.2 - Таблица истинности элемента НЕ

При подаче логических единиц путём замыкания ключей и через транзисторы около этих ключей протекает достаточный ток и на входе в инвертирующий транзистор поступает достаточное напряжение для его открытия, ток свободно течёт, сопротивление инвертирующего транзистора невелико, напряжение падает на резисторе при инверторе, на выходе логический нуль.

При подаче на ключи или единицы или нуля, или обоих нулей, выходного напряжения в инвертор не достаточно для его открытия, его сопротивление велико и на его коллекторе образуется высокий уровень напряжения, на выходе логический нуль.

Схема элемента И-НЕ со сложным инвертором представлена на рисунке 1.5.

Рисунок 1.5 - Элемент И-НЕ со сложным инвертором

Таблица истинности для данного элемента соответствует таблице 1.3.

Данный элемент состоит из трёх каскадов: входной (R1, VT1,VT2 - модель многоэмиттерного транзистора), фазоинверсный (VT3, R2, R4) и выходной усилитель (VT4, VT5, VD3, R3).

При подаче на входы x 1 и x 2 логических единиц возникает коллекторный ток на транзисторах VT1,VT2 и втекает в базу транзистора VT3, открывая его. Часть тока эмиттера VT3 поступает в транзистор VT5, он открывается, на выходе y устанавливается низкий уровень напряжения, при этом VT4 закрыт (недостаточно напряжения через переход база-эмиттер VT4 и VD1). При подаче хотя бы одного логического нуля, коллекторный ток транзисторов VT1, VT2 прекращается, VT3 и VT5 закрываются, VT4 открывается. Так как VT5 закрыт на выходе образовывается высокий уровень напряжения.

Синтез и исследование элементов на МДП-транзисторах.

Развитие компьютерной схемотехники на основе МОП-транзисторов началось с появлением в 1962 г. полевого транзистора с индуцированным каналом. Схемы на МОП-транзисторах характеризуются относительной простотой изготовления, компактностью, малой потребляемой мощностью, высокой помехоустойчивостью к изменению напряжения питания. МОП-транзисторы имеют структуру: металл-диэлектрик-полупроводник и в общем случае называются МДП-транзисторами. Поскольку диэлектрик реализуется на основе оксида SiO 2 , то применяют название МОП-транзисторы (униполярные, канальные). Металлический электрод, на который поступает управляющее напряжение, называется затвором (З) а два других электрода -- истоком (И) и стоком (С). От истока к стоку протекает рабочий ток. Для р-канала полярность стока отрицательная, а для п-канала -- положительная. Основная пластина полупроводника называется подкладкой (П). Канал -- это приповерхностный проводящий слой между истоком и стоком, в котором величина тока определяется с помощью электрического поля.

Процессы инжекции и диффузии в канале отсутствуют. Рабочий ток в канале обусловлен дрейфом в электрическом поле электронов в n-каналах и дырок в р-каналах.

При нулевом значении управляющего напряжения канал отсутствует и ток не протекает. Канал, который образуется под действием внешнего управляющего напряжения, называется индуцированным. Напряжение, при котором образуется канал, называется пороговым. Канал с начальной дополнительной концентрацией зарядов называется встроенным. Быстродействие n-МОП транзисторов в 5-8 раз выше быстродействия р-МОП транзисторов, поскольку подвижность электронов существенно больше дырок. В МОП-схемах полностью исключены резисторы, их роль выполняют МОП-транзисторы.

Элемент ИЛИ-НЕ,.

Схема элемента ИЛИ-НЕ изображена на рисунке 1.6.

Рисунок 1.6 - Элемент ИЛИ-НЕ на МОП-транзисторах

Транзистор VT1 выполняет роль резистора так как МОП-транзисторы обладают высоким сопротивлением, для того, чтобы он пропускал ток, исток подключен к положительному полюсу источника. При одновременной подаче на транзисторы VT2 и VT3 логических нулей, происходит их закрытие, они создают нагрузку после транзистора VT1, уровень этого напряжения соответствует логической единице. Таблица истинности данного элемента соответствует таблице 1.1. Если на вход будет подана хотя бы одна или обе логических единиц, один из транзисторов VT2 и VT3 (или оба) откроются, произойдет спад напряжения, на выходе буде логический ноль.

Элемент И-НЕ.

Элемент И-НЕ представлен на рисунке 1.7.

Рисунок 1.7 - Элемент И-НЕ на МОП-транзисторах

Элемент ИЛИ.

Элемент И.

Синтез и исследование элементов на КМДП структурах.

Элемент ИЛИ-НЕ.

Элемент И-НЕ.

Синтез и исследование элементов на основе эмиттерно-связанной логики (ЭСЛ).

Схемотехника элементов ЭСЛ основана на использовании дифференциального усилителя в режиме переключения тока. Элементы ЭСЛ появились в 1967 г. и в настоящее время являются самыми быстродействующими среди полупроводниковых элементов на основе кремния. Задержки распространения сигналов в элементах ЭСЛ уменьшились до субнаносекундного диапазона (приблизительно 1 нс).

Сверхбыстродействие элементов ЭСЛ достигается за счет использования ненасыщенного режима работы транзисторов, выходных эмиттерных повторителей, малых амплитуд логических сигналов (около 0,8 В). В логических элементах ЭСЛ имеется парафазный выход, что позволяет одновременно получать прямое и инверсное значение реализуемой функции. Это дает заметное снижение общего количества микросхем в аппаратуре.

Особенностями схемотехники ЭСЛ и ее характеристик являются:

Возможность объединения выходов нескольких элементов для образования новых функций;

Возможность работы на низкоомную нагрузку благодаря наличию эмиттерных повторителей;

Небольшое значение работы переключения и независимость потребляемой мощности от частоты переключения;

Высокая стабильность динамических параметров при изменении температуры и напряжения питания;

Использование отрицательного источника питания и заземления коллекторных цепей, что уменьшает зависимость выходных сигналов от помех в шинах питания.

К недостаткам элементов ЭСЛ относят сложность схем, значительное потребление мощности и трудности согласования с микросхемами ТТЛ и ТТЛШ.

Элемент И.

Элемент ИЛИ.

Элемент И-НЕ.

Элемент ИЛИ-НЕ.

Синтез и исследование элемента НЕ на МДП-транзисторах () в положительной и отрицательной логике.

СЕРГИЕВ ПОСАД

Логические функции, ЭЛЕМЕНТЫ и схемы

Цель работы

Исследование логических функций, логических элементов и схем.

Приборы и элементы

Логический преобразователь.

Генератор слов.

Вольтметр.

Логические пробники.

Источник напряжения + 5 В.

Источник сигнала "логической единицы".

Двухпозиционные переключатели.

Двухвходовые элементы И, И-НЕ, ИЛИ, ИЛИ-НЕ.

Микросхемы серии 74.

Краткие сведения из теории

Аксиомы алгебры логики

Переменные, рассматриваемые в алгебре логики, могут принимать только два значения - 0 или 1. В алгебре логики определены отношение эквивалентности (обозначается знаком =), операции сложения (дизъюнкции), обозначаемая знаком , умножения (конъюнкции), обозначаемая знаками &, или точкой, и отрицания (или инверсии), обозначаемая надчеркиванием или апострофом ".

Алгебра логики определяется следующей системой аксиом:

x = 1, если x 0; x = 0, если x 1;

0&0 = 0; 1 1 = 1

1&1 = 1; 0 0 =0;

1&0 = 0&1 = 0; 0 1 = 1 0 = 1;

Логические выражения

Запись логических выражений обычно осуществляют в конъюнктивной или дизъюнктивной нормальных формах. В дизъюнктивной форме логические выражения записываются как логическая сумма логических произведений, в конъюнктивной форме – как логическое произведение логических сумм. Порядок действий такой же, как и в обычных алгебраических выражениях. Логические выражения связывают значение логической функции со значениями логических переменных.

Логические законы и тождества

При преобразованиях логических выражений используются следующие логические законы и тождества

Логические функции

Любое логическое выражение, составленное из n переменных с помощью конечного числа операций алгебры логики, можно рассматривать как некоторую функцию n переменных. Такую функцию называют логической. В соответствии с аксиомами алгебры логики функция может принимать в зависимости от значения переменных значение 0 или 1. Функция n логических переменных может быть определена для 2 n значений переменных, соответствующих всем возможным значениям n-разрядных двоичных чисел Основной интерес представляют следующие функции двух переменных х и у

f 1 (x,y) = x & y = x y = x – логическое умножение (конъюнкция),

f 2 (x,y) = x y – логическое сложение (дизъюнкция),

f 3 (x,y) = = – штрих Шеффера,

f 4 (x,y) = = – стрелка Пирса,

f 5 (x,y) = x y = – сложение по модулю 2,

f 6 (x,y) = ![]() – равнозначность.

– равнозначность.

Логические схемы

Физическое устройство, реализующее одну из операций алгебры логики или простейшую логическую функцию, называется логическим элементом. Схема, составленная из конечного числа логических элементов по определенным правилам, называется логической схемой. Основным логическим функциям соответствуют выполняющие их схемные элементы.

Таблица истинности

Так как область определения любой функции n переменных конечна (2 n значений), такая функция может быть задана таблицей значений f(i), которые она принимает в точках i, где i= 0,…,2 n -1. Такие таблицы называют таблицами истинности. В таблице 1 представлены таблицы истинности, задающие указанные выше функции.

Таблица 1

| Значения переменных | ||||||||

| x | у | f 1 | f 2 | f 3 | f 4 | f 5 | f 6 | |

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 2 | 1 | 0 | 0 | 1 | 1 | 0 | 1 | 0 |

| 3 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 |

Карты Карно

Если число логических переменных не превышает 5-6, преобразования логических уравнений удобно производить с помощью карт Карно. Цель преобразований - получение компактного логического выражения (минимизация). Минимизацию производят объединением соседних наборов (термов). Объединяемые наборы должны иметь одинаковые значения функции (все 0 или все 1). Для наглядности рассмотрим пример: пусть требуется найти логическое выражение для мажоритарной функции f m трех переменных x, у, z, описываемой таблицей истинности, показанной в Таблице 2.

Таблица 2

Мажоритарная функция

| № | x | y | z | f m |

| 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 | 1 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 1 | 0 | 1 | 1 |

| 6 | 1 | 1 | 0 | 1 |

| 7 | 1 | 1 | 1 | 1 |

Здесь номер строки равен числу i= 2 2 x+2 1 y+2 0 z, образованному значениями переменных.

Составим карту Карно. Она представляет собой нечто похожее на таблицу, в которой наименования столбцов и строк представляют собой значения переменных, причем переменные располагаются в таком порядке, чтобы при переходе к соседнему столбцу или строке изменялось значение только одной переменной. Например, в строке xy таблицы 3 значения переменных xy могут быть представлены следующими последовательностями 00,01,11,10 или 00,10,11,01. Таблицу заполняют значениями функции, соответствующими комбинациям значений переменных. Полученная таким образом таблица выглядит, как показано ниже (таблица 3).

Таблица 3

Карта Карно

мажоритарной функции

xy  z z

| 00 | 01 | 11 | 10 |

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 1 | 1 |

На карте Карно отмечаем группы, состоящие из 2 k соседних ячеек (2,4,8,) и содержащие 1, так как они описываются простыми логическими выражениями. Три овала в таблице определяют логические выражения xy, xz, yz. Каждый овал, объединяющий две ячейки, соответствует логическим преобразованиям:

Компактное выражение, описывающее функцию, представляет собой дизъюнкцию полученных при помощи карт Карно логических выражений. В результате получаем выражение в дизъюнктивной нормальной форме

f m = xy v xz v yz .

Если объединять 0, то получим выражение в конъюнктивной нормальной форме

f m = (x v y)(x v z)(y v z).

При реализации мажоритарной функции трех логических переменных получим схему, которая при подаче на ее входы трех сигналов сформирует на выходе сигнал, равный сигналу на большинстве входов (2 из 3 или 3 из 3). Эта схема применяется для восстановления истинного значения сигналов, поступающих на 3 входа, если возможна ошибка на одном из входов.

Для реализации этой функции на элементах 2И-НЕ необходимо провести следующие преобразования:

Для ДНФ получилось более простое выражение, поэтому его и следует реализовать. Соответствующая схемная реализация приведена на рис. 1.

|

Рис. 1

ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ

Отправить свою хорошую работу в базу знаний просто. Используйте форму, расположенную ниже

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

HTML-версии работы пока нет.

Cкачать архив работы можно перейдя по ссылке, которая находятся ниже.

Подобные документы

Основные аксиомы и тождества алгебры логики. Аналитическая форма представления булевых функций. Элементарные функции алгебры логики. Функции алгебры логики одного аргумента и формы ее реализации. Свойства, особенности и виды логических операций.

реферат , добавлен 06.12.2010

Системы цифровой обработки информации. Понятие алгебры Буля. Обозначения логических операций: дизъюнкция, конъюнкция, инверсия, импликация, эквивалентность. Законы и тождества алгебры Буля. Логические основы ЭВМ. Преобразование структурных формул.

презентация , добавлен 11.10.2014

Булевы алгебры – решетки особого типа, применяемые при исследовании логики (как логики человеческого мышления, так и цифровой компьютерной логики), а также переключательных схем. Минимальные формы булевых многочленов. Теоремы абстрактной булевой алгебры.

курсовая работа , добавлен 12.05.2009

Свойства операций над множествами. Формулы алгебры высказываний. Функции алгебры логики. Существенные и фиктивные переменные. Проверка правильности рассуждений. Алгебра высказываний и релейно-контактные схемы. Способы задания графа. Матрицы для графов.

учебное пособие , добавлен 27.10.2013

Основы формальной логики Аристотеля. Понятия инверсии, конъюнкции и дизъюнкции. Основные законы алгебры логики. Основные законы, позволяющие производить тождественные преобразования логических выражений. Равносильные преобразования логических формул.

презентация , добавлен 23.12.2012

Основные понятия алгебры логики. Дизъюнктивные и конъюнктивные нормальные формы. Сущность теоремы Шеннона. Булевы функции двух переменных. Последовательное и параллельное соединение двух выключателей. Свойства элементарных функций алгебры логики.

контрольная работа , добавлен 29.11.2010

Понятие алгебры логики, ее сущность и особенности, основные понятия и определения, предмет и методика изучения. Законы алгебры логики и следствия из них, методы построения формул по заданной таблице истинности. Формы представления булевых функций.

учебное пособие , добавлен 29.04.2009